电子技术论坛

信息来源: 时间:2020-11-24

CMOS版图设计概要基本步骤和解析

1、隔离环

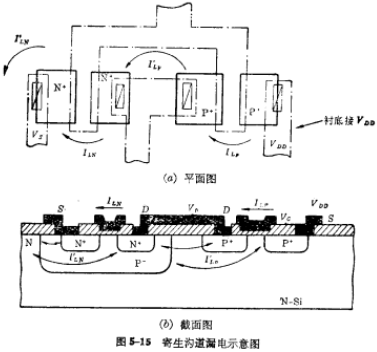

CMOS是微功耗电路,对功耗的要求特别严格。造成功耗大的主要因素是静态泄漏电流。因此,在工艺和版图设计时,特别要注意采取适当措施,使漏电尽可能减到最小。CMOS版图设计概要。图5-15所示为产生漏电的主要途径。其中 分别表示负载管和输入管沟道以外的氧化层下面的漏电;

分别表示负载管和输入管沟道以外的氧化层下面的漏电; 和

和 分别表示P+源(或P+漏)与P-阱,N+源(或N+漏)与N-衬底之间寄生MOS管漏电。

分别表示P+源(或P+漏)与P-阱,N+源(或N+漏)与N-衬底之间寄生MOS管漏电。

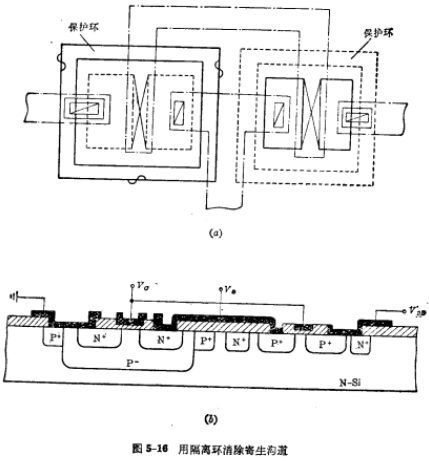

要消除寄生漏电,必须在版图设计时采用隔离环,以中断寄生沟道。图5-16所示是用与衬底同类型的扩散环包围有源器件。在P-阱区扩散P+隔离环,以截断寄生的N型沟道,在N-衬底上扩散N+隔离环,以截断P型寄生沟道。

从图中可以看到,在两个N+和P+隔离环之间的区域是不会发生寄生的泄漏沟道的。所以这些区域是互连线的安全区。CMOS版图设计概要。因为要在高浓度扩散环上引起寄生的反型层,需要很高的电压,而实际电路的电源电压要比场致开启电压低得多,从而消除了寄生漏电的途径。

2、绘图尺寸规定

(1)图形标记

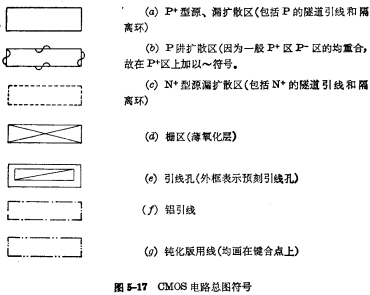

CMOS通常有六块掩膜图形:即①P阱扩散区图形;②P沟道MOS管原漏及P+隔离环扩散区图形;③N沟道MOS管源漏及N+隔离环扩散区图形;④栅和引线图形;⑤接触孔(引线孔)图形;⑥金属电极图形。

根据原四机部关于CMOS电路联合设计会议规定,目前CMOS电路的总图所采用的符号如图5-17所示。

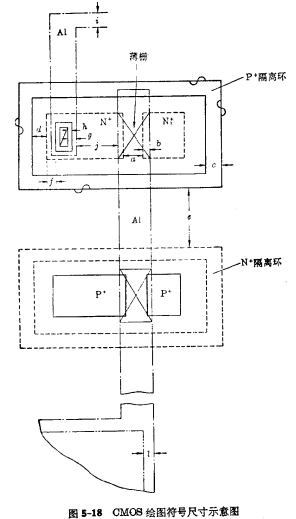

(2)版图最小尺寸

版图设计中的最小尺寸与工艺水平有关。下列版图尺寸,并不代表当前工艺水平,只供读者参考。

小规模电路(单位:μm)

(a)沟道长10;(b)栅覆盖(每边)5;(c)扩散区条宽12.5;(d)扩散区间距12.5;(e)P阱与N隔离环间距20;(f)引线孔距扩散区边缘7.5;(g)铝覆盖引线孔5,引线孔10×12.5;(h)预刻引线孔每边比孔大2.5;(i)铝条宽12.5;(j)铝条间距12.5,键合点120×120,键合点间距120;(k)键合点至管芯边间距100;(l)钝化版比铝键合点每边小7.5,芯片分割线至管芯间距300。

小规模电路一般可用500倍比例绘制原图。CMOS版图设计概要。中规模电路可用800倍比例或400倍比例绘制原图。中规模电路的最小尺寸比小规模电路略有缩小,如:为道长8~10;扩散区宽8~10;引线孔距扩散区边缘5,铝覆盖引线孔2.5~3,引线孔8×12。

上列各种基本尺寸及绘图符号在图5-18中标明。

3、高件图形举例

根据计算得到的器件尺寸及图形标记和绘图尺寸规定,就可以绘制各器件的配置图。

(1)二输入端“或非”门配置图

图5-19为二输入端“或非”门配置图的实例。这样的配置图,器件排列比较规则,布线比较整齐,充分利用了晶片面积。

(2)CMOS传输门配置图

图5-20为CMOS传输门的配置图。图中把CMOS传输门的N管和CMOS倒相器的N管放在一个P-阱内,可以节省晶片面积。

4、栅保护器件

CMOS电路与单沟道电路一样,在输入端也必须加保护电路,因此在图形设计时必须加以考虑。CMOS电路常用的保护电路一般有两种形式。

(1)单二极管保护电路

这种保护电路的二极管联接方法有两种形式,一是把二极管接在输入端与地之间,如图5-21所示;另一种是把二极管接在输入端与电源之间,如图5-22所示。

(2)电阻二极管保护电路

图5-23为电阻二极管保护电路的形式,在图中,D1为N+型扩散在P阱上形成的二极管,击穿电压 为P+型扩散在衬底上形成的二极管,击穿电压

为P+型扩散在衬底上形成的二极管,击穿电压 为保护电阻,是P型扩散在N型村底上形成的扩散电阻,这个电阻本身也形成二极管D2,所以不必单独制作,R的数值在500~1000Ω之间。

为保护电阻,是P型扩散在N型村底上形成的扩散电阻,这个电阻本身也形成二极管D2,所以不必单独制作,R的数值在500~1000Ω之间。

CMOS电路总图绘制的步骤及其它一些原则,与单沟道MOS电路类同,这里不再细述。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助