电子技术论坛

信息来源: 时间:2020-11-24

CMOS阈值电压的设计装置与流程

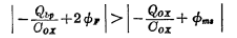

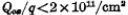

要使设计的电路版图在性能上达到设计指标的要求,必须进行工艺设计,从而确定合理的材料参数、工艺参数和工艺条件。其中,阀值电压的控制是CMOS电路工艺设计的核心。CMOS阈值电压的设计。因为,一方面要保证NMOS管增强型工作,即 ;另一方面,要求NMOS和PMOS管的阈值电压尽可能匹配,即

;另一方面,要求NMOS和PMOS管的阈值电压尽可能匹配,即 ;其它材料参数和工艺参数许多是根据

;其它材料参数和工艺参数许多是根据 的要求定出来的,所以在这里主要介绍阈值电压的设计。至于材料参数和工艺参数及工艺条件,将在下一章中分别介绍。

的要求定出来的,所以在这里主要介绍阈值电压的设计。至于材料参数和工艺参数及工艺条件,将在下一章中分别介绍。

1、保证NMOS管为增强型

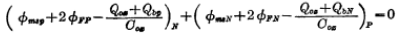

在第一章中讲到,要使NMOS管为增强型工作,必须要求:

所以,在工艺上要采取措施,尽可能减小 和适当提高Qw,但P阱区的掺杂浓度

和适当提高Qw,但P阱区的掺杂浓度 不能提得很高,它要受到击穿电压的限制。CMOS阈值电压的设计。按目前的工艺条件,

不能提得很高,它要受到击穿电压的限制。CMOS阈值电压的设计。按目前的工艺条件, 可控制在

可控制在 左右;P阱的掺杂浓度应大于

左右;P阱的掺杂浓度应大于 。

。

2、VT的匹配

CMOS电路要有高的抗干扰性能和良好的开关特性,两管的阀值电压必须良好的匹配,即:

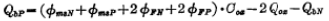

由这一条件可得到下面的表达式:

所以可解得:

上式括号内的数值,在 和

和 一定范围内通常是常数;式中

一定范围内通常是常数;式中 很小,通常对匹配影响极小,而

很小,通常对匹配影响极小,而 可由

可由 来控制。这样,就可以认为

来控制。这样,就可以认为 主要以

主要以 为变数。

为变数。

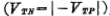

由上式可知, 和

和 完美匹配条件将是

完美匹配条件将是 和

和 的线性函数关系,可以作出如图5-24中斜虚线所示的N沟道和P沟道器件的设计匹配线。CMOS阈值电压的设计。该图是在

的线性函数关系,可以作出如图5-24中斜虚线所示的N沟道和P沟道器件的设计匹配线。CMOS阈值电压的设计。该图是在 一定,

一定, 时作出的。由图可得出以下两点:

时作出的。由图可得出以下两点:

①N沟道和P沟道器件阈值电压匹配的设计点在匹配线上 ,对于每个匹配设计点,它是

,对于每个匹配设计点,它是 和

和 的函数,即是P阱扩散浓度和表面电荷的函数。

的函数,即是P阱扩散浓度和表面电荷的函数。

②由匹配线可见,当表面电荷 较大时,就要求有很高的P-阱扩散浓度。但这种极低电阻率的P型衬底扩散是不容易控制的,且高浓度扩散将造成N沟道器件电子迁移率的严重下降;况且,高的

较大时,就要求有很高的P-阱扩散浓度。但这种极低电阻率的P型衬底扩散是不容易控制的,且高浓度扩散将造成N沟道器件电子迁移率的严重下降;况且,高的 使得P沟道器件的

使得P沟道器件的 升高,从而使CMOS开关速度降低,同时要求采用较高的电源电压。根据匹配线来设计时,只有当

升高,从而使CMOS开关速度降低,同时要求采用较高的电源电压。根据匹配线来设计时,只有当 时,方能得到阈值电压的良好匹配。

时,方能得到阈值电压的良好匹配。

综上所述,要制作一个阈值电压良好匹配的CMOS电路,工艺要求是严格的。因为对应匹配线上每个设计点,仅有一个 及

及 的值,所以CMOS工艺是对电路特性最敏感的工艺。CMOS阈值电压的设计。对于一个特定的CMOS工艺规范,应该是P-阱扩散的薄层电阻数值有良好的重复性,栅氧化表面电荷

的值,所以CMOS工艺是对电路特性最敏感的工艺。CMOS阈值电压的设计。对于一个特定的CMOS工艺规范,应该是P-阱扩散的薄层电阻数值有良好的重复性,栅氧化表面电荷 数值要小,且重复性良好。因此对CMOS工艺提出了严格的净化要求。否则,要达到完美匹配是困难的。

数值要小,且重复性良好。因此对CMOS工艺提出了严格的净化要求。否则,要达到完美匹配是困难的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助