电子技术论坛

信息来源: 时间:2022-8-26

MOSFET器件隔离-小型化(按比例缩小)的器件隔离原理及结构

MOSFET器件隔离

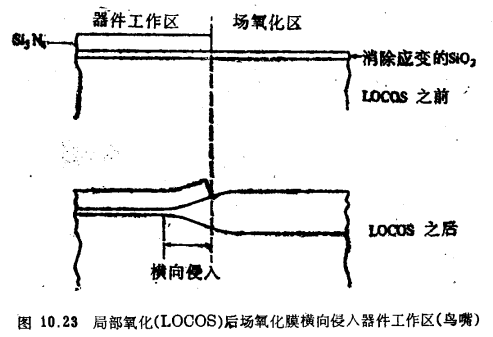

集成电路工艺中,MOSFET器件隔离是器件设计的一个组成部分。最广泛使用的隔离技术是硅的局部氧化技术,缩写为LOCOS,在10.3节已作了讨论。LOCOS中的主要问题示于图10.23。

可以看到,LOCOS会使氧化膜横向侵入器件工作区(壕沟),侵入的距离可以与生长的场氧化膜厚度相比,结果形成所谓“鸟嘴”。MOSFET器件隔离。因为,不想增大多晶硅与硅之间以及金属与硅之间的(寄生)电容,场氧化膜的厚度就不能再减小,因而,横向侵入的长度就无法减小到比某一定的最小值还小,这个值大约为0.8μm左右。有一些工艺可以减小横向侵入,目前正在研究之中,可以替代标准的LOCOS工艺,这些工艺是所谓的侧壁掩膜隔离(SWAMI),密封界面局部氧化(SILO)和有选择的外延生长(SEG)。MOSFET器件隔离这些工艺比LOCOS还要复杂,介绍这些工艺已超出本章的范围。在别处可以找到关于器件隔离技术的很好的评述。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助