电子技术论坛

信息来源: 时间:2022-8-26

MOSFET沟道区-小型化(按比例缩小)的沟道区原理及结构

MOSFET沟道区

沟道区由四个主要部分构成:衬底、硅到绝缘膜的界面、栅绝缘膜和栅电极,因为沟道区是所有器件进行工作的地方,因此在器件设计中自然地会对它引起相当大的注意。当然,在衬底中主要的问题是掺杂,它同时决定了器件的阈值电压和它对偏置的灵敏度(或因此缺少)。MOSFET沟道区。在5.8节讨论过,沟道中用一次或多次注入来凋整掺杂水平和掺杂分布,从而可满足按比例缩小的要求。这些注入或者通过栅绝缘膜进行,或者在该处的绝缘膜形成以前进行。例如,在10.3节讨论的工艺流程的例子中,所谓阈值电压调整的注入和耗尽注入都通过栅SiO2进行。如10.2节所讨论的,接着进行的高温工艺流程足以对SiO2和Si晶格损伤进行退火,并且活化这些注入剂。MOSFET沟道区。但是,通过栅绝缘膜进行注入的方法,由于过多的操作带有露着绝缘膜的硅片,因此会带来一些损害栅绝缘膜质量的危险。

实际上,现在所有制造出的MOSFET,栅绝缘膜是在硅表面上热生长的二氧化硅,其它的绝缘膜尚在进行实验研究,主要是热生长的氮化硅或氮氧化硅。但是,SiO2继续表现出与硅形成最好界面,这里“最好”的意思是指界面具有很低浓度的界面固定电荷和陷阱(界面态)。因为界面电荷不利于载流子的表面迁移率,所以,低电荷密度是很重要的。相当大的努力致力于发展热氧化工艺,想要制造出厚度均匀的薄氧化膜,这种氧化膜具有低的界面电荷密度、低的体内陷阱浓度、低的缺陷密度和高的击穿电压。当氧化膜厚度按比例缩小后,所有这些氧化膜的性能受到严重地挑战。

MOSFET用的主要的栅材料是n+掺杂多晶硅。因为这一层相当多地用来形成互连导线,所以有很高的积极性来降低它的电阻率。因为多晶硅一般是简并掺杂的,通常它的体电阻率是最小的可能值。当一般厚度为0.4μm左右时,n+掺杂多晶硅的电阻率引起的薄层电阻为每方20到30Ω。现在,高熔点金属硅化物淀积在掺杂多晶硅的顶层形成一个混合的栅电极,称为多晶硅化物。MOSFET沟道区。厚度与n+掺杂多晶硅相同的多晶硅化物的薄层电阻要小5到10倍。因为与栅氧化膜接触的仍旧是多晶硅,多晶硅化物栅电即具有与多晶硅一样的电学特性(如功函数)。当然,这是很有利的, 因为对多晶硅来说已经有了相当丰富的生产经验。因此,多晶硅化物是很希望采用的,而且在发展过程中,已经把它们结合到IC的制造工艺中了。MOSFET沟道区。尽管如此,在一些孤立的情况下,甚至在工业生产中,正在进行通过把高熔点金属直接淀积在栅氧化膜上形成栅电极的实验。这方法的好处是相对于多晶硅化物来说,栅的薄层电阻又减小10倍,但是这种新材料要求在工艺上作相当大的改进。

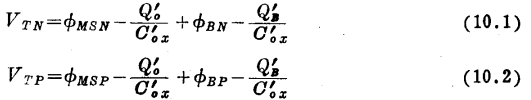

除了与栅电极材料电阻率有关的问题以外,现在,要着重说明一下CMOS工艺中,器件小型化时栅电极与硅的接触电势的重要性。明确地说,我们已知,恒定电场换算时器件的阈值电压;VT必须相应的缩小。MOSFET沟道区。当然,目前,在恒定电压条件下,实际的按比例缩小,大约已进行到有效沟长度约为0.6μm。但是,有一点小的疑问,就是如果尺寸进一步按比例缩小,则电压还需要降低。当电压降低时,VT将不得不相应地按比例缩小。当L<0.5μm,电源电压必须在3V左右以避免由于向氧化膜中注入热载流子而引起的不稳定。MOSFET沟道区。这时,CMOS中n-沟和p-沟器件的阈值电压分别必须约为0.5V和-0.5V。现在考虑这样的器件如何来做。按(2.5.29),二个阈值电压可写为

式中所有的符号已在第2章中定义过,下标N和P分别代表n-沟和p-沟。首先考虑具有n+多晶硅栅电极的n-沟器件。于是,典型值为ΦMSN≈-0.85V和ΦBN≈0.75V。因为,对于这一假设下的按比例缩小的器件来说,氧化层厚度将是非常薄,假定0.015μm,则C´ox就非常大,对一般的Q´o值来说,可以略去Q´o/C´ox。这一项。则(10.1)为

在第6章中已经见到,体电荷Q´B[由式(2.5.27)给出]一般可通过离子注入来调节,因此可以得到所希望的VTN。一般的衬底掺杂浓度NA≈103μm-3。(预先注入),接近Si-SiO2界面处的NA还需要增加些。MOSFET沟道区。如在10.3节已看到的,这可通过注入硼来完成。这道工序的作用不仅使VTN增大到所希望的值,而且也提高了衬底的掺杂浓度,因而降低了VTN对漏偏置电压的灵敏度(5.4节)。

从以上讨论明白了用对称的工序来调整p-沟器件的阈值电压是所希望的。如果PMOS器件的栅材料是p+掺杂多晶硅,则不难看出这将如何来做。这时(10.2)为

其中Q´B/C´ox是很小的正值。于是,通过向沟道中注入磷或砷,使Q´B再正些,就可得到所希望的VTNP值,并且可增加漏偏置电压的抗扰性。但是,在CMOS工艺中,同时使用n+和p+掺杂多晶硅尚未证明能实际使用。MOSFET沟道区。原因是,通过金属来连接这两种类型的多晶硅所需要的欧姆接触区域是非常费空间的。另一方面,在多晶硅化物工艺中,用重叠起来的硅化物把这两种类型的多晶体连起来(搭接)已经证明是不实际的。虽然,对n+到少多晶硅的接触来说,不需要有专门的区域,但是已发现硅化物搭接会引起掺杂原子在多晶硅中非常快速的扩散,其结果会在相邻的n-沟和p-沟晶体管中,多晶硅掺杂类型会发生完全反型。MOSFET沟道区。这一使人烦恼的现象目前正在研究之中,而且可能会发现解决的办法。然而,工艺设计师们眼下暂时还不得不或是用n+多晶硅,或是用p+多晶硅。主要的选择还是n+多晶硅,但是已经发表了一些p+多晶硅的研究报告。

假定用n+掺杂多晶硅,式(10.2)成为

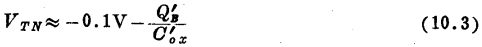

如使VTP近似为-0.5V,不难看到,必须使Q´B为负!这意味着要向衬底注入相反类型的杂质。MOSFET沟道区。当然,它要导致一个埋-沟器件(6.3节)。遗憾的是,这种类型的器件具有不良的断路特性和不良的漏偏置电压的抗扰性。因此,它不能作成与表面沟道器件一样短的沟道。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助