电子技术论坛

信息来源: 时间:2022-8-25

MOSFET源区-小型化(按比例缩小)的源区原理及结构

由于不断地改进集成电路的制造工艺,有可能通过不断减小器件尺寸来增加电路的密度和提高电路的速度。5.8节介绍了小型化对器件特性影响的结果并讨论了按比例缩小的方法学。MOSFET源区。本节将要考虑在探求使器件不断小型化时所遇到的制造上的问题和困难。然而,重要的是要看到还有一些这里没有考虑的但与整个电路小型化有更普遍联系的其它一些问题也是很值得注意的。这些问题主要与互连线的小型化有关,而且,在某些情况下,会成为小型比的主要的有决定性的因素。

如5.8节所讨论的,正确的小型化要求所有的尺寸程度不同地—致按比例缩小。这样,当横向尺寸减小时,薄层的厚度(高度)必须相应地减小。MOSFET源区。参照以前的图10.5,把MOSFET的主要特征区分为:源、漏、沟道区和与相邻的电路元件的隔离。从讨论中将会看到,与这些特征区中的每一个相联系的,都有具体的小型化问题。

MOSFET源区

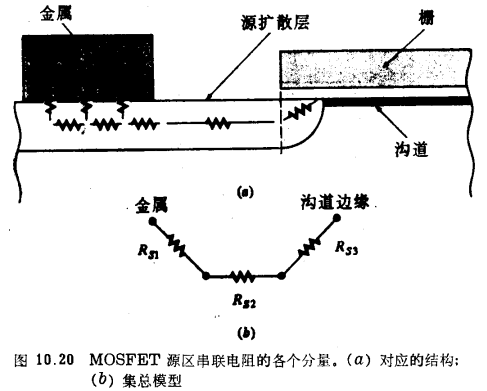

MOSFET源区的主要要求是从与金属接触处到沟道的边界之间的电阻一定要小,而且在沟道的边界处,它还必须是一个向沟道发射载流子的有效发射体。对大多数常规的结构来说,这二个要求是有密切联系的,因为高电导的源区也是一个有着丰富的沟道中所要求的那种类型的载流子的区域。满足了一个要求,通常也会满足另外一个要求,因此,这二个要求可以合而为一,即,与沟道电阻相比,源区电阻必须可以忽略,不然,器件特性就会严重下降。对大多数实际应用来说,L有效≈0.5μm和dox≈0.2μm,源区总串联电阻为300~500Ω•μm(Ω乘以μm宽度)是合适。参考图10.20,总串联电阻是金属与n+或p+层之间的接触电阻Rs1、上面的边界与栅和沟道接触的边界之间的薄层电阻Rs2、和后者的边界与沟道边界之间的扩展电阻Rs3之总和。MOSFET源区。Rs1是集总电阻,包括“真正”的接触电阻和在扩散层中由于电流积聚引起的电阻。根据按比例缩小理论,减小源扩散层(结)深度,那么源区串联电阻的所有分量都要增加,这是由于必须要减少总掺杂剂量所致,这种减少在PMOS器件中特别严重,因为在硅中用来形成p+区的硼的特性比那些用来形成n+区的砷更不适宜。特别是,即使加速能量很低,硼向硅中注入时也趋向于注入得比较深,这是由于通过硅晶格时称为离子的沟道作用现象所致。这一现象对砷来说并不那么严重,砷原子比硼原子要重得多,因而,趋向于很容易破坏晶格的有序性,从而破坏了它本身的成沟概率。MOSFET源区。再有,硼是一个比砷要快得多的扩散源,所以,在源-漏区注入后,在各种所需的高温工序下,很难保持浅的p+层。

对常规制造的源区,例如,象图10.20所示的那样,经过砷和硼注入、退火和扩散,对n+来说,结深限制在0.15到0.30μm,对p+ ,为0.35到0.65μm,对应的薄层电阻为每方100到30Ω和每方150到80Ω。虽然薄层电阻只是与源区总电阻的一个分量,即Rs2直接有关,但其它二个分量也有跟踪薄层电阻的倾向。

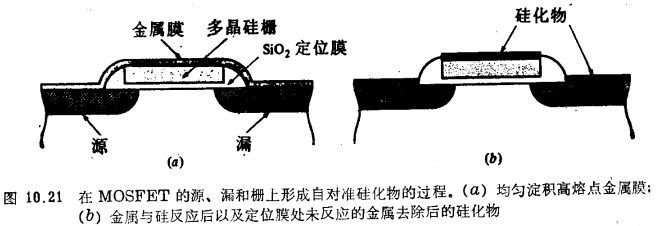

当维持浅结时,我们已经作出了很大的努力来冲破对源区电阻的这一限制。或许最有希望的方法是把很浅的离子注入和很短时间的退火相结合,然后,在露出的硅表面上形成自对准的硅化物。MOSFET源区。从图10.21可以看到, 这一工艺要求在多晶硅栅极的两端用一绝缘的定位膜。在重掺杂硅和多晶硅顶部的薄氧化膜去除掉,均匀淀积一薄层高熔点的金属(如Ti,Ta,W等),如图10.21a所示。然后把硅片置于适当地高温下(600~800℃)金属与硅反应生成二硅化物(如TiSi2)。MOSFET源区。但是,在定位膜处,因为该处没有硅原子可提供,所以那里的金属未经反应,故可以很容易的用金属的择优腐蚀去除掉,最后在裸露区域形成自对准的硅化物,如图10.21b所示。这个工艺不仅可以得到高电导的源区(和漏区),也可以得到高电导的栅极,薄层电阻可降低5到10倍,而且,由于定位膜,寄生的源-栅和漏-栅电容也降低了。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助