电子技术论坛

信息来源: 时间:2022-8-3

MOS晶体管非本征部分的小信号的栅重迭电容解析

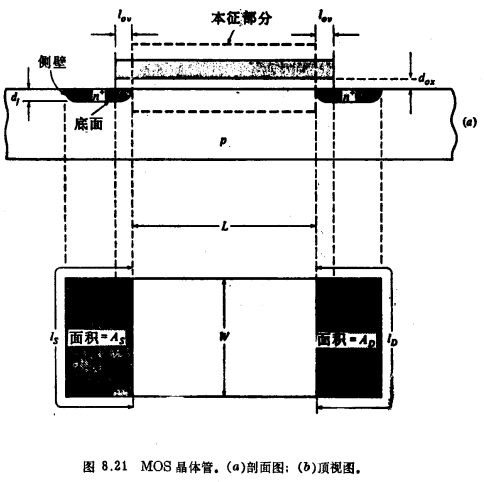

晶体管的“非本征”部分是指图8.21a虚线以外的所有部分。在图8.21a及顶图8.21b中,我们给出了在下面讨论中要用到的一些符合的定义。

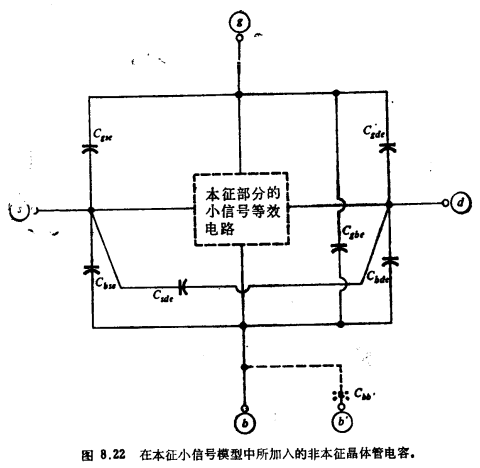

与非本征部分有关的电荷存储效应可用6个小信号电容来模拟(每一对端子之间有一个电容,如图8.22所示)在用于这些电容的符号中,前两个下标指明有关的器件端,下标c代表非本征的。MOS晶体管非本征部分的小信号。若晶体管恰巧在CMOS芯片上的阱内,那末,还要考虑由于阱和公用衬底(阱就在它上面形成)之间的pn结而形成的电容。在图8.22中,这一电容记作Cbb´,其中b对应于晶体管的本体,b´对应于公用衬底。虚线框内表示本征部分的模型,这一部分已在前两节讨论过了。现在,我们把注意力集中在这七个非本征电容上。如下面所讨论的那样,不难把每个电容和晶体管的物理结构联系起来。

栅重迭电容

栅和两个n+区之间的重迭总是不可避免的。这就产生了“重迭电容”。由于栅和n+区都是高浓度掺杂的,故这类电容可用近似为线性的平板电容器 来模拟,氧化层作为电介质。MOS晶体管非本征部分的小信号。如果重迭长度为ιov,如图8.21所示,栅宽是W,则忽略边缘效应(即由于场强线不是垂直表面,而是沿着重迭区之外的边缘而产生的效应)以后,我们有

来模拟,氧化层作为电介质。MOS晶体管非本征部分的小信号。如果重迭长度为ιov,如图8.21所示,栅宽是W,则忽略边缘效应(即由于场强线不是垂直表面,而是沿着重迭区之外的边缘而产生的效应)以后,我们有

如果ιov很小,则由于边缘场强线而引起的电容可使总电容值增加一个很大的百分数。MOS晶体管非本征部分的小信号。这就牵涉到边缘电容得计算问题,并常常采用经验估算。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助