电子技术论坛

信息来源: 时间:2022-8-1

MOS晶体管本征部分的中频小信号等效电路解析

当施于MOS晶体管的小信号电压快速变化时,小信号端电流会大大地不同于图8.2电路所预测的电流。现在我们采介绍一种简单模型,该模型可预测这时的电流特性,只要小信号电压的频率不是太高。MOS晶体管本征部分的中频小信号。通过假设准静态工作,并考虑到电荷存储效应,可使该模型实现这一点。并非所有电荷存储效应都包括在这一模型中;另外的一些电荷存储效应将在第9章中考虑。然而,将要在这里介绍的模型就其本身的合理性来说是重要的,并且由于以下两个原因,我们将以独立的方式来介绍它:

1、该模型使用广泛,因为它在精度和复杂性之间实现了一种合理的平衡。—些读者也许发现它适合于他们的用途,所以觉得在遇到有用的模型之前不必非要采用第9章中的一般处理方法。

2、这一节的内容是第9章中一般处理方法的有用的基础。事实上,只要通过对将在这里推导的模型加上一些额外的元件便可得到第9章中的更加完整的模型。

如上所述,本节中我们栘只考虑晶体管的本征部分。不明显地指出这一点,渎者也会理解的。非本征器件的建模将在8.4节中介绍。

本节中,我们强调直观分析。若要求更加严格—些,则读者只得等到介绍第9章内容的时候。

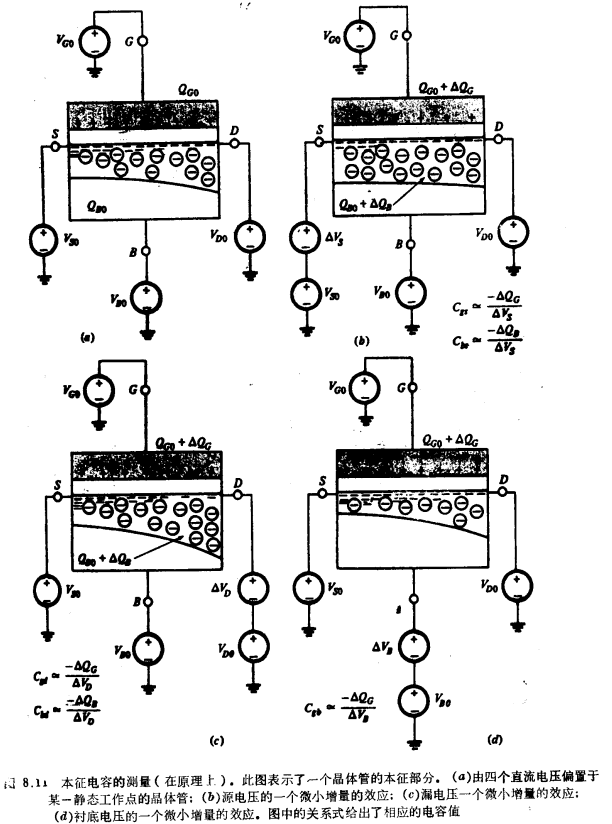

MOS晶体管本征电容

长沟道晶体管的本征部分(忽略了紧靠源区和漏区的二维效应)可认为是一个源区和漏区的长度已缩短为零的假想器件,如图.11a所示,如果我们把四个端上的电压都定义为相对于一个任意点(图中用“接地”符号表示),则讨论将会更方便些。下标0将用来表示图8.11a中的电压和电荷的值。现在让我们来考虑Vs的微小变化对栅电荷和耗尽区电荷的影响(图8.11b),VD的微小变化对栅电荷和耗尽区电荷的影响(图8.11c),以及VB的微小变化对栅电荷的影响(图8.11d)。MOS晶体管本征部分的中频小信号。这些图中的细节及图旁的定义式下面立刻就要说明。这三幅画是假定ΔVs、ΔVD和ΔVB代表增加量而画成的。假设变化前后,电压都是恒定的,且图8.11中的所有情况都处于直流稳态。因此,例如图8.11b中的ΔQG就是源端电压固定为Vs+ΔVs时的总稳态电荷与源端电压固定为Vs时稳态电荷之差。为简单起见,界面电荷Qo没有表示出来。

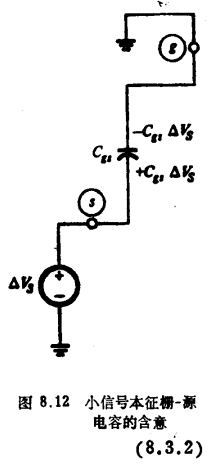

现在来详细考虑图8.11b的实验。各点上,氧化层两端的电势差相对于图8.11a来说减小了,因而栅电荷减少了,所以ΔQG是负的。原因(ΔVs)和效应(ΔQG)之间的关系, 可以用图8.12的小信号等效电路来表示。在这一电路中,电压ΔVs在电容底极板上放置了电荷CgsΔVs,在顶极板上放置了电荷CgsΔVs。由于电荷-CgsΔVs。表示图8.11b中电荷的变化ΔQG,故必有-CgsΔVs=ΔQG。因此,Cgs=ΔQG/ΔVs,如图8.11b旁边所注。更正规一些,可写为

重要的是不要把Ggs同图8.11中的任何平板结构联系起来。Cgs仅仅是图8.12中的假想电容所应有的值,以便使假想电容顶极板上的电荷与图.11b中的电荷变化ΔQG相同。注意,由于当ΔVs为正时,ΔQG为负,故Cgs的值是正的。

图8.11b也况明了源对衬底的电容效应。增大Vs使耗尽区的宽度增加。因此,使那里的总电荷更负。所以ΔQB是负的。这是靠更多的受主原子电离(与图8.11a相比)来实现的。这意味成负电荷∣ΔQB∣的空穴通过衬底端离去;这可等价地说成负电荷ΔQB从衬底端进入器件。根据上面所说的理由, 定义

增加VD的效应完全类似于增加VS的效应,并已在图8.11c中说明。我们定义

最后,增加VB的效应说明在图8.11d中。增加VB引起正电荷流进衬底端,这些电荷部分地由QG的减少来平衡。QG的减少与负的刀ΔQG流进栅的说法是等价的。在弱反型时(此时,反型电荷可以忽略),这一点是不难理解的。MOS晶体管本征部分的中频小信号。于是, 所有正的电荷变化ΔQB实际上必定由栅电荷的相反变化来平衡。因此ΔQG将是负的。我们定义

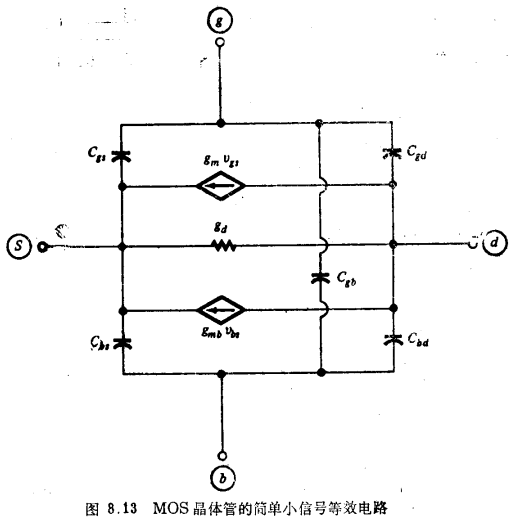

所有上面五种效应都可用类似于图8.12的方式来模拟,在图8.2的电路中,通过加入五个电容就可把这些效应计入小信号等效电路,如图8.13所示。重要的是要注意,在最终所得到的模型中,各个元件间互不干扰。例如,把g、d和b等端接地,在s端施加的ΔVs将引起电荷-CgsΔVs进入g端。这样就正确地模拟了源对栅的影响。与栅相连的Cgd和Cgb不会干扰上述影响,因为它们现在所起的作用相当于开路(跨接在它们两端的电压是固定不变的)。读者不难检查,其余四个申容效应中的每一个效应也刊用与其他电容互不干扰的对应电容来模拟。这种“无干扰”是一个很重要的特性,该特性应该在这样的情况下细心地检查:每一次把几个元件——每一个意味着模拟一个单独的效应——连接在一起以组成一个电路模型。由于Cgs、Cgd和Cgb表示其他三端中的每一端正栅上的效应,故图8.13电路可以在注意观察一个MOS晶体管的栅时,准确地模拟准静态小信号效应。注意,我们现在不准备对其他端证明类似的论述(这个问题将在第9章中进一步讨论)。此时,我们将只说,通过与更完整的模型(第9章)相比较得知,图8.13的拓扑结构是令人满意的(就观察任意一端而言,以及就考虑任意一端对另一端的影响而言);即使端电压随时间连续变化,但只要其变化足够慢,该拓扑结构仍是满意的。对于正弦规律的微小变化,图8.13电路可以定量化,方法是:对电路模型建立一个有关其有效性的上限频率。这一上限频率所取的值,取决于所要求的精度,工作区域,对哪一端加激励信号,要考虑哪些端电流,是不对这些电流的幅值和相位都感兴趣,①等等。因此,很难给出一个单一的数。然而,通过与更高级的模型拓扑结构朴比较。可给出一些通用的提示。这样,在强反型时,不论采用什么标准,模型有效性的上限频率结果正比于(但不等于)下面这个量:

至于这里存在等号右边这个量的原因,在第9章讨论了更高阶的模型以后就会明白。因此,假定在低频时,所有模型元件都具有令人满意的值,于是在不修改这些元件值的情况下,模型将继续有效直到频率约为0.1ωo。(一个保守的极限,对于十分临界应用的极限)或甚至到0.5ωo。(对于非临界应用)。这一性能在许多情况下已是足够的了。注意,随着频率的增加,模型性能的变坏是逐渐的,故观察不到在任意一个特定频率时性能“明显地”变坏。MOS晶体管本征部分的中频小信号。在高频情况下,模型最终变得不可接受,这将不是因为元件值不正确,而是因为模型(图8.13)的本质不适合于高频。在这种情况下,实现满意的建模的唯一方法是采用第9章中所讨论的更高级的模型拓扑结构。

上面定义的五个电容强烈地依赖于端电压中的“偏置电压值”,也就是在它们附近出现小信号电压的那些值。图8.11a中,这些偏置电压由VD0,VG0,VB0和VS0表示。为简单起见,从现在起,将把它们记作VD,VG,VB和VS。现在来介绍以偏置电压表示的电容表达式。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助