电子技术论坛

信息来源: 时间:2022-6-28

MOS晶体管沟道长度调制效应时特性曲线详解

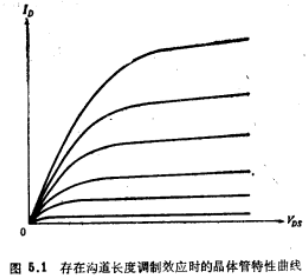

正如4.4节中所提到的,在饱和区内,ID-VDS特性并不完全平行于横轴,而是具有正的斜率。并且发现当其他条件均相同时,沟道越短,这一斜率越大,并可能较易觉察,如图5.1所示。在历史上,这一现象是被研究的第一“短沟道效应”。原先并不是这样分类的,对它这样命名的原因部分是因为在认识到其他各种短沟道效应之前,对它的研究已很充分;另一部分原因是它在电路分析工作中起着重要作用,甚至当器件的沟道较长时(例如10μm或更长)也是如此。

饱和时漏附近区城内的二维分析提供了一幅极为复杂的电场图。场强线从漏n+区出发,终止于沟道上的一些点。有些线是近乎水平的,但另有一些线从n+区的底部出发,且方向朝下,然后渐渐地弯曲向上,最后终止在反型层。另外,场强线还从栅到沟道,再从沟道到体内,并在靠近漏区时以复杂的形状弯曲。电子浓度朝着漏区的方向递减,并且这些电子被从表面推开而进入体内。因此,我们可以认为沟道在漏区附近是向下弯曲的,并且在那里电流是在“次表面”的路径中流动的。根据这样一幅场图,我们可以猜测,漏结的深度会影响电流值,事实上,确实如此。

对于上述的复杂场图,至今不能提供简单的解析模型。然而已经研究出许多半经验的公式。有时为了获得有关饱和区特性的近似而又易处理的结果,采用了大大简化后的图,这就是现在将要描述的。图5.2a表示一个品体管的半导体部分,其中VDS=VˊDS,VˊDS是假设沟道漏端出现4.4节中所说的“夹断”现象时的VDS值。在那一节中已解释过,在此假设下,漏端处的lQˊIl值较小但不为零,它比在漏端处单位面积耗尽区电荷的值要小得多。若VDS在VˊDS之上再增加,则漏端区的lQˊIl将减小到低于上述值。这时反型层的夹断点将往左移如图5.2b所示,并且可把夹断点和漏n+区之间的区域近似为一个耗尽区。在这样一幅近似图中,耗尽区假设只是近似的,这并不意味着电流等于零。读者可能熟悉pn结和双极型品体管,在那里大电流可以通过耗尽区。但是,由于在这里所说的耗尽区内lQˊIl较小,故为了使ID能有一显著的值,必须假设电子在其中以高速运动。

在图5.2b中,沟道不能承受大于VˊDS的电压,这是由于沟道两端的电压达到此值时,沟道就被夹断了。于是,过剩的电压VDS-VˊDS必须降落在漏区和沟道的夹断点之间。这样一个非零电压只可能存在于长度∆L不为零的区域上,如图所示。若VDS进一步升高,必定有更多的过剩电压降落在耗尽区两端。为了承受这个电压,耗尽区必然变宽,而反型层在长度上将有一些收缩。这就称为沟道长度调制。如果耗尽区内的电子浓度很小,则我们可以假设该区内的所有电荷实际上都由体密度为NA的电离受主形成。在耗尽区左端沿x方向的沟道场强值记作E1,然后假设耗尽区内靠近表面处的场强线近似是水平的,利用泊松方程(1.2.13)可以证明,耗尽区的长度∆L与降落在它两端的电势差VDS-VˊDS有如下关系

其中

按照这一简单模型,电流导通的机制如下:电子进入源端并沿沟道运动;在沟道的夹断点,它们发现自己所处的实际上是一个耗尽区。如从图5.2b所见,该区内的场强方向是要把电子扫过耗尽区到达漏。注意,上述一维模型完全忽略了极为重要的栅对漏区附近电场的影响。

另一种公式表示法认为,夹断出现在当漏附近的场强高到足以引起速度饱和①的时候(假设一个有关电子速度的简化模型,在此模型中。速度饱和是当场强为某一有限值时突然达到的)。当VDS高于速度饱和时的相应值时,假定电子在耗尽区内以最高速度运动。这种表示法得出的公式还是式(5.2.1)和(5.2.2),其中E1是这样一个场强值,高于此值,电子速度假设就饱和了。在有些方法中,认为夹断对应于这样一点,此时反型层如二维模拟所预计的那样“潜入”界面之下。这一点可以更精确地定义为表面场强的垂直分量变为零的点。对于图5.2b中器件的方位,栅场把紧靠界面的反型层“拉”向夹断点之左,同时把界面之下的反型层“推”向夹断点之右。这种表示法得出的公式还是式(5.2.1)和(5.2.2),但是E1必须根据数值解求出。实际上,不管对夹断采用何种定义,通常最终总是按经验调整式(5.2.2)中的E1值,以获得与实验结果的最佳吻合。为简单起见,有时在1和20V/μm之间取一个值用作B1。

现在让我们来考虑这些现象对漏端电流的影响。在VDS=VˊDS时,电流IˊD通常从非饱和公式算出,这些公式假定一直适用到VDS=VˊDS这一点。根据这样一些计算[例如参看式(4.4.19)和(4.4.17)]可知

式中的比例系数(常数)取决于VGS和VSB。

现在考虑大于VˊDS的某个VDS值,并令对应的电流为ID。考虑图5.2b中未夹断的那部分沟道,可以计算出这个电流。那部分沟道的情况与图5.2a相同,只是L现要用L-∆L来代替,因此与式(5.2.3)类似,有

从上述两公式可得:

式(5.2.1)所预计的∆L/L值为

上面的推导指出,式中的B1=(2∈3/q)1/2。然而实际上,B1和ФD可以是按最后所得的ID表达式与实验数据之间能最佳吻合而选择的经验参数。甚至有一种更简单的公式表示法得出ФD=0,但是这样一种公式表示法是以夹断点的场强E1=0这一不正确的假设为基础的。还有一个问题是,随着VDS减小并趋向于VˊDS时,这种表示法预计斜率dID/dVDS趋向于无限大。

式(5.2.5)和(5.2.6)所预计的饱和电流,其误差在许多应用场合下都是可以接受的。但是可能有这样一种情况,即ID的误差较小,而与此同时斜率dID/dVDS的误差却较大,特别是在dID/dVDS本来就较小的情况下。这一点将在8.2.2书中详细讨论。当正确预测dID/dVDS成为至关重要时(例如在模拟电路设计中),上述模型可能是不合适的。这时可能不得不采用更精确的(及复杂得多的)分析方法,这些分析方法计及栅对夹断区内电场的影响,也计及夹断区内的非零值电荷和反型层的形状。这样一种分析方法预期可导出下列∆L表达式的一般形式:

式中r为漏结深度。为导出上述形式的结果,需要进行二维或准二维分析,并且也要采用某种简化(回想一下,∆L所隐含的整个思想就是简化)。若干这样的分析方法已介绍在文献中,尽管并非所有方法都考虑了上面提及的每一效应。

有些参数,例如VT,VˊDS,载流子的最大速度,甚至反型层的厚度等,有时也作为参数出现在∆L的表达式中,尽管原则上这些参数都是式(5.2.7)右边各量的函数。在附录J中给出了两个有关这种分析结果的例子。

对于数字电路设计来说,饱和区的dID/dVDS本身常常并不重要,故由于计算速度的原因,上一段中所提到的复杂结果应避免采用。事实上,有时采用比式(5.2.5)和(5.2.6)更为简单的模型,这些模型指出ID与VDS的相关性是一次的。为了把这类简单模型与上述模型联系起来,让我们把式(5.2.6)代入(5.2.5),并把所得之式在VDS=VˊDS附近展开为泰勒级数,且只取前两项。结果为

及

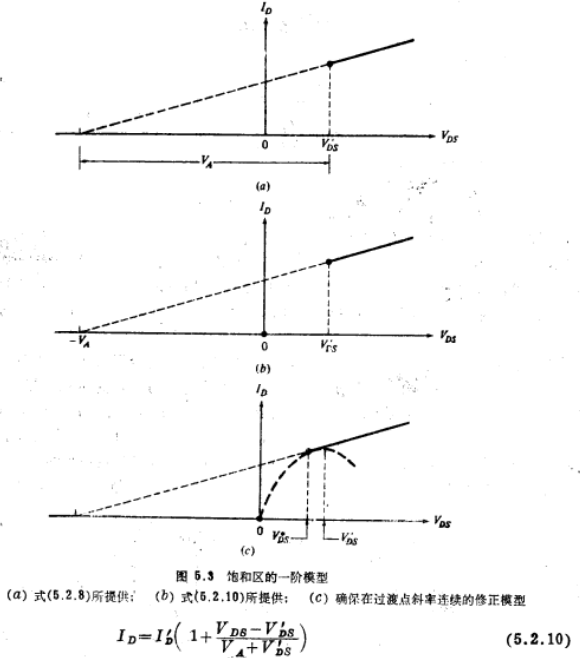

其中B2是比例常数,其值的范围是0.1至0.2Vμm1/2。式(5.2.8)绘于图5.3a。横轴的截距为-VA+VˊDS,因此它通过VˊDS与VGS相关。使用中的另外一个经验模型是:

此式的图形裁横轴于-VA点,如图5.3b所示,它与VˊDS无关。因此假设对应于各个不同的VGS值的饱和曲线都是直线,这些直线如果延长,则彼此相交在横轴上的同一点。在采用某些制造工艺的实际器件中,可能会近似地观察到这种特性。对于这一模型中的VA,已提出了一种简便的计算方法

此式具有式(5.2.9)的函数形式。

注意,上述饱和曲线预示在VˊDS处的斜率不为零,而非饱和公式却预测在上述点的斜率为零。这种斜率的不连续性并非本来的属性,而且也是用于电路的计算机模拟的数值算法所不希望有的。为了避免这一问题,可把饱和曲线画成与非饱和曲线相切,如图5.3C所示。所以,饱和与非饱和之间的分界点就被定义在VDS点略左一些的地方,在图5.3c中用 表示。

表示。

例5.1让我们根据非饱和公式(4.4.30a)和饱和公式(5.2.10)来推导一种模型,不过由于上面所考虑的原因,式中的VDS用 代替。于是,有

代替。于是,有

及

式中, 是式(5.2.12)在它适用范围的上刚点处的电流值,即

是式(5.2.12)在它适用范围的上刚点处的电流值,即

现在,令从式(5.2.12)和(5.2.13)分别得到的dID/dVDS相等,就可求得使斜奉连续所要求的 值。结果为

值。结果为

从图5.3c的图形结构可预期,随着VA趋向无限大, 应趋近于VˊDS。用式(5.2.15)不难检查出,情况确是这样(题5.3):随着VA趋向无限大,ˊ趋近于(VGS-VT)/(1+δ),该值实际上就是不考虑沟道长度调制的模型中的VˊDS值参看式。

应趋近于VˊDS。用式(5.2.15)不难检查出,情况确是这样(题5.3):随着VA趋向无限大,ˊ趋近于(VGS-VT)/(1+δ),该值实际上就是不考虑沟道长度调制的模型中的VˊDS值参看式。

我们再次强调,式(5.2.8)和(5.2.10)仅仅对近似预测饱和区的漏端电流ID来说是两个好的公式。但对于那些要求准确预计斜率dID/dVDS的应用场合(例如,对于模拟电路),这些公式完全是不适用的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助