电子技术论坛

信息来源: 时间:2022-5-27

解析二端MOS结构-平带电压及其寄生电荷组成

二端 MOS结构-平带电压

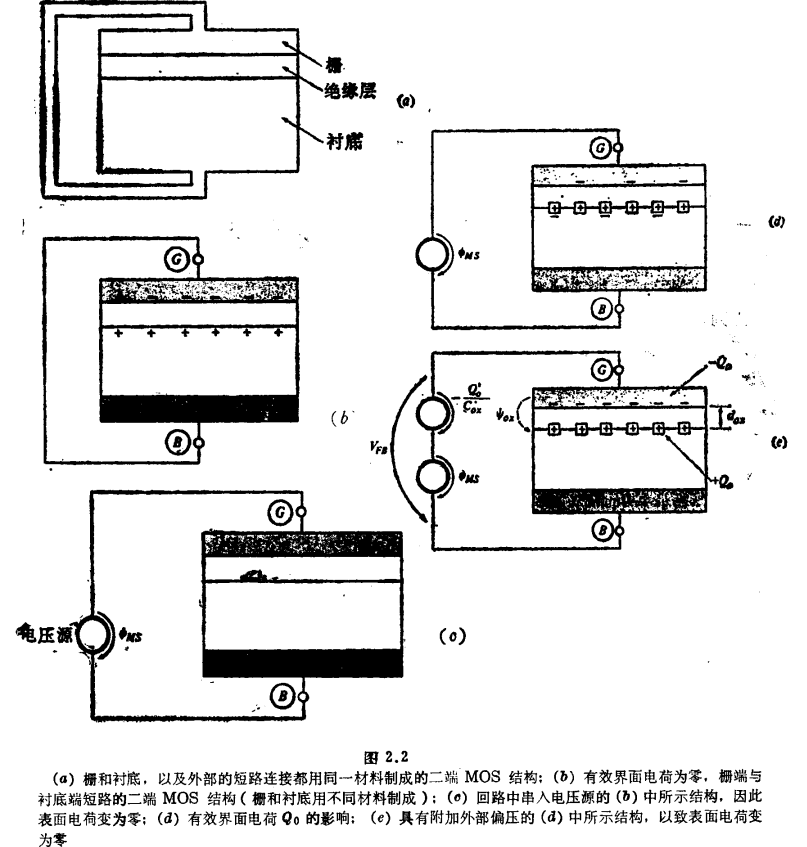

我们从一种“纯理论”的情况(见图2.2a)开始讨论。这里假定栅与衬底用掺杂浓度一样的同一种结晶材料(现在的情况下是p型硅)制成,并假定用同样材料设法把栅连向衬底,在某种意义上使得栅成为衬底的延伸。在硅中未画有电荷,因为p型材料中的每个带正电的空穴对应着一个产生该空穴的带负电的受主原子,而且也不存在使空穴在任一特定区域内堆积起来的原因。所以电荷互相抵消,而材料到处是电中性的。图2.2α的结构基本上是对称的,若假定在制造过程中没有引入寄生电荷,则在绝缘层中不会有电场,因而也就不会把载流子吸引到绝缘层-衬底界面上去。

下面考虑如图2.2b所示的实际情况。栅由某种材料制成而不需要与衬底材料相同,用一种金属与栅材料接触,从而构成如图所示的栅端G。以后将用下标G表示栅端而不是栅本身。本体(衬底)的背面被一块金属板接触,如图所示,该金属板再依次与某种金属接触,于是构成体端B。同样,下标B将用来表示体端,如图所示,而不是体材料本身。

现在我们用一根导线把栅端与体端短路,如图所示。然后考虑从栅材料经外部连线至体材料的路径上所遇到的几个接触电势。然而,根据1.4节中的讨论已知,接触电势的总和只决定于第一种和最后一种材料,而与中间任何一种材料都无关。利用式(1.4.7)有

从栅经外部连线至体内所有接触电势之和=Φ栅材料-Φ体材料(2.2.1)

式中右边的每一个量是相应材料的特征量,这在1.4节中已讨论过。栅材料和衬底之间电势差不为零造成了在氧化层两边出现净电荷。例如,若电势差为负,则这些电荷的极性将如图2.2b所示。

现在来考虑下面这样一个问题:能否通过外加一个电压而使这些净电荷消失?这种情况见图2.2c。为了使从栅材料经外部连线至体内的总电势差为零,则必须使外加电源电压精确地与接触电势之和相抵消。从式(2.2.1)可见,电源电压的值必为

式中ΦMS是广泛采用的符号;ΦMS的值可根据上式和表1.1计算出来①。在无外部偏压时,接触电势的影响并不是在衬底内产生净电荷浓度的唯一起因,另一个原因是“寄生”电荷,这类电荷不仅在氧化层内部而且在氧化层-半导体界面上都可能有。

寄生电荷由四部分组成[1]:

1、氧化层固定电荷

存在于紧靠氧化层-半导体界面处。这种电荷起因于氧化层的生长机制,是在氧化结束时留下的,它与氧化层厚度,掺杂类型(n或p)以及掺杂浓度无关。

2、所谓氧化层陷阱电荷

可在整个氧化层内存在,但通常位于靠近氧化层与衬底或与栅的界面上。这种电荷来源于幅射、光电发射或者从衬底注入高能量载流子(见5.6节)。

3、可动离子电荷

可存在于氧化层内部,它起因于来自环境的碱性离子(常常是钠)的污染。在外电场作用下,这种电荷能在氧化层内移动。

4、界面陷阱电荷(也称快表面态电荷)

存在于氧化层-半导体界面上。它起因于界面上的某些缺陷,这些缺陷产生电荷“陷阱”;它们能和半导体交换可动载流子。起着象施主或受主那样的作用。

上述这些电荷起初阻碍了高性能MOS器件的发展,因为对它们的本质还不十分了解,而且也难于控制。例如在早期,上面提到的可动离子电荷的数量大,且在氧化层内的漂移取决于外加电压和温度。这种电荷往往是在生产过程中通过加工器件的人的手传递到氧化层中来的,它会导致器件出现一些极难控制的特性。今天,经过多年努力以后,通过现代生产技术,已使上述四类电荷大为减少[1]。全书中,我们假定所讨论的器件都是采用这种现代技术生产出来的。在未作进一步说明之前,我们将假定所有寄生电荷都处在氧化层-半导体界面上,而且其值(用Qo表示)是固定不变的②。如果有些器件在氧化层内部存在不可动电荷(沿图2.2中的水平面作均匀分布),则在模拟这些器件时,可设想这种电荷不存在,但相应地调整Qo值(习题2.18);于是,Qo可看成为有效界面电荷。这种电荷无论对p型n或型衬底几乎总是正的。在现代器件中,有效界面离子的面密度约为200~1000个离子/μm2,相应的有效界面电荷密度是0.032~0.16fC/μm2。

在图2.2d中,有效界面电荷Qo画在小方块之内。在此图中,若用一个电压为ΦMS的电池去抵消前面讨论过的接触电势的影响,则便可研究QO本身的影响了。由于电中性的需要,Qo将在系统中感应出相反的总电荷-Qo,如图2.2d所示。电荷-Qo的一部分将出现在栅上,另一部分将出现在半导体内。如果希望消除这些电荷,人们可能会注意到,若能在栅上提供全部所需的平衡电荷-Qo,那么,在半导体内就不会感应出电荷来了。为了在栅上提供-Qo,可在外部电路中串联一个电池,其(一)端和栅相连。根据静电学基本知识(附录B),显然可得出如下结论:由于在氧化层的栅一边和衬底一端必定分别有电荷-Qo和Qo,因此从栅经氧化层到衬底的氧化层两端的电势降落ψox必等于-Qo/Cox,式中Cox为氧化层两端间的总电容。ψox正是电池必须提供的电压值,如图2.2e所示。

若用单位面积上的量Q′o和C′ox来表示图2.2e中的ψox,则有

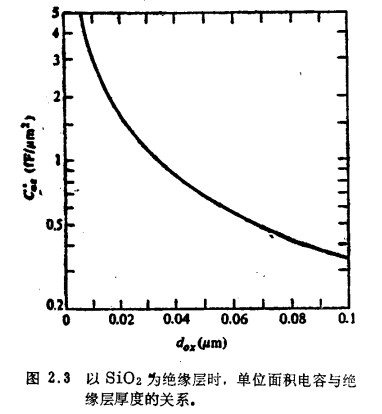

单位面积氧化层电容可用下式给出(附录B)

式中dox为绝缘层厚度,∈ox是它的介电常数,由下式给出:

其中∈o为真空介电常数(8.854×10-3fF/μm),κox为绝缘层的相对介电常数。对于SiO2,κox=3.9。式(2.2.4)绘于图2.3中。

因而现在已可看出,一个加在栅端和衬底端之间的外部电压可以抵消接触电势和Q′o的影响,从而使半导体处处保持中性。这一电压称为平带电压①,记作VFB。从图2.2e可得平带电压的表达式为:

例2.1 铝栅工艺。有一由p型衬底(NA=5000μm-3)SiO2(厚度dox=0.042μm)和铝栅构成的MOS结构,试计算其平带电压。等效界面电荷Q′o为0.1fC/μm2。

利用式(1.4.1)可得衬底的费米势等于0.33V。

根据式(2.2.2)和表1.1,有

根据式(2.2.4),C′ox=0.822fF/μm2,因而

-Q′o/C′ox=-0.12V。于是,用式(2.2.6)可得

例2.2 硅栅工艺。若用n型多晶硅栅(ND=103μm-8)代替上例中的铝栅,试估算平带电压(如在第10章中讨论的那样,当用硅材料做糖时,这种“硅栅工艺”有许多优点)。

多晶硅的性质尚未完全了解,在MOS分析工作中,通常采用由测量间接获得的特征值,或者假定栅改用单晶硅制成,然后用上述方法估算出平带电压。我们采用后一种方法。由于给定的掺杂浓度很高,所以栅材料是简并的,它的费米势可近似取为-0.56V(见1.4节)。计算中用到的其他数值均与前例相同。这样,根据式(2.2.2),有

然后,应用式(2.2.6),可得

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助