电子技术论坛

信息来源: 时间:2022-5-20

高速低温CMOS电路性能及其温度变化解析

高速低温CMOS电路性能

CMOS电路的抗闩锁(Latch-up)性能也与温度密切相关。

Latch-up的产生是由于杂散npn和pmp双极管之间的正反馈所致。当温度降低时这些双极管的电流增益β会大大降低。以垂直杂散双极管为例,在室温下β=230,降至液氮温度77K时β减至为4,在4.2K下β为0.4。因此,在低温下工作的CMOS集成电路几乎不存在Latch-up问题,由此解决了CMOS电路设计和应用中的一个难题。

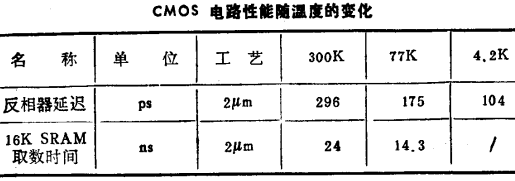

用反相器和16K SRAM进行实验的结果如下表。

由上表可见,在低温下CMOS电路的速度可提高一倍。用1μm工艺可达更快的速度。

近来,在77K下的超导薄膜技术的研究取得了突破性进展;同时有些科学工作者发现某些金属硅化物,如CoSi2,在低温下也具有超导特性。正如我们在第二章中所指出的,在VLSI电路中连线的分布参量延迟已成为影响电路速度的主要因素。如采用在77K下具有超导性能的薄膜作为CMOS VLSI的连线,可以大大改善性能。因此,在低温下CMOS与超导技术的结合在超高速应用领域内具有良好的前景。近来,美国IBM公司已经用0.5μm工艺研制成在77K下取数时间3.5ns超高速64K CMOS SRAM,这证实了上述的科学预测。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助