电子技术论坛

信息来源: 时间:2022-5-19

三种高速的BiCMOS集成电路及其工艺技术解析

1、基本逻辑电路

用CMOS构成基本逻辑,用两个Bipolar管作为末级推挽输出,高速驱动大的电容负载。

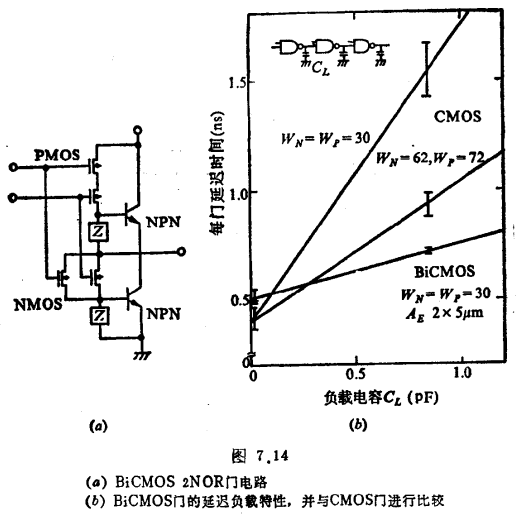

图7.14为BiCMOS 2NOR门电路图以及在不同电容负载CL下的延迟时间的测量结果,并与一种2μm CMOS门电路的结果进行比较。电路图中Z表示阻性元件。由图可见,负载电容CL越大,BiCMOS电路的优越性越大。

2、SRAM

超高速tAC=8ns的BiCMOS的256K SRAM已研制成功,而普通用1μm工艺CMOS SRAM的tAC为20ns左右。

加快这种BiCMOS SRAM的要点是利用双极管跨导大的特点降低读出时位线的电平摆幅,以减少充放电时间,并用多级双极型差分放大器进行放大,加快SRAM的读出速度。

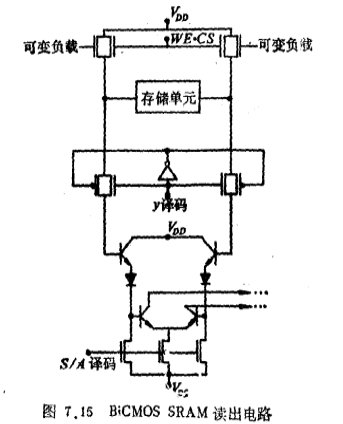

图7.15为BiCMOS SRAM的一种读出电路。其中存储单元电路仍采用多晶硅电阻负载的低功耗NMOS单元。位线的负载是可变的。当读出时所有4个负载管均打开,呈低阻状态,由此限制位线的电平摆幅在50mV左右。

3、超高速运算电路

用2um BiCMOS已研制成主频为60MHz的32位微处理器电路。该电路中CMOS器件占95%,而Bipolar仅占5%。Bipolar只用于驱动大负载电容和放大小的电平摆幅讯号。

图7.16为ALU中的4位一组的进位传输电路。图中ф2,为预充时钟。由于Bipolar的存在,预充电平决定于EB结的正向压降。预充电平约降为0.8V左右,电平摆幅的减少,有利提高此电路的运算速度。Si、Ci为各位加法器运算出的本位数和进位数。

在ф1时钟周期内,Si、Ci从各加法器送至进位传输电路,Cout通过一个Bipolar放大输出。32位字长的ALU要求有8个这样的进位传输电路,其总延迟时间只有7.2ns,功耗也只有十几毫瓦。

在控制电路中的BiCMOS微码ROM,用Bipolar作为地址译码驱动器的末级和灵敏放大电路,使ROM的取数时间大大加快。设计的微码ROM的容量为2K×64,其取数时间tAC为17ns。

由此可见,BiCMOS技术对加快CPU的的速度是十分有效的,而且由于所用的双极管比例很少,因而仍可保持CMOS电路低功耗的特点,所以它被认为是继CMOS工艺之后最现实的下一代高速VLSI工艺技术。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助