电子技术论坛

信息来源: 时间:2022-5-16

GaAs高速集成三种电路图及其改进优缺点分析

1、缓冲型逻辑(BFL)

图7.4为BFL的电路图,它全由D MESFET组成。T1、T2,和T3构成一般的或非门,但它们都是常通管,因此这一级不能输出好的低电平。为此,由T4、T5和D1、D2,构成缓冲输出级,其低端接一个负电源Vss,使电平向低方向移动。由D1、D2上的压降及Vss来调节低电平,使它小1V,这样使输出和输入电平相容。

附加的缓冲级除了移动电平作用外,还有增加驱动能力的功能,但有增大功耗的副作用。由此看来,BFL电路具有高速度、强负载能力及高功耗的特点。每门延迟为30ps左右,功耗为5~10mW左右。根据上述特点,它不适用于LSI及VLSI,而主要用于超高速的中、小规模集成电路。

2、Schottky二极管FET逻辑(SDFL)

图7.5为SDFL的一级门电路。它由二极管和DFET所组成。由D1、D2、D3,和T1组成一级或门,它的低电平接近Vss,使下级反相器的驱动管T3,可以关闭。

SDFL门用非常小的二极管执行“或”功能,又实现电平移动。功能级和反相级都不象BFI那样常通,因此功耗大大降低,约为BFL的1/5左右,速度仅降低2倍左右。

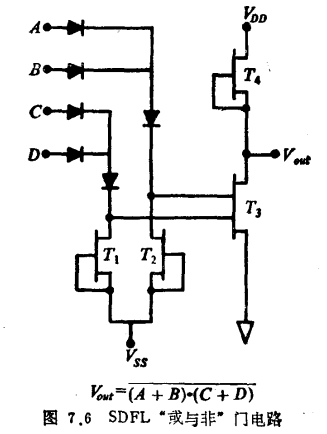

SDFL由于性能较好,普遍应用于各种高速电路。图7.6为SDFL的“或与非”门电路,其中T3是双栅管,起着“与”的作用。

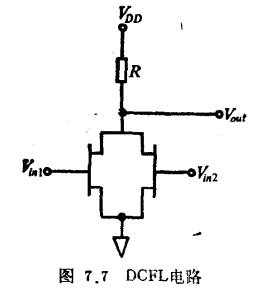

3、直接耦合FET逻辑(DCFL)

用E FEY组成的DCFL如图7.7所示。它的特点是电路十分简单,面积小,不需要电平移动,功耗也很低,每门约为50μW。在速度方面比BFL慢2~4倍。该电路形式适用于VLSI。

以上三种逻辑电路形式各有其优缺点,因而适用于不同的领域。

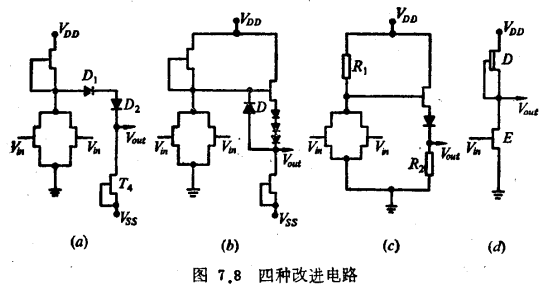

在上述电路形式的基础上,还有不少改进形式,图7.8画出其中比较重要的四种典型。

图7.8(a)是把BFL的源跟随驱动级去掉,换成由D1、D2和T4组成的电平移动级,因而大大降低功耗,但也降低了输出级的电流驱动能力。这种电路主要用于扇出比较少的内部电路。

图7.8(b)是用一个反向二极管作为BFL驱动级的加速电容,使BFL达到更高的速度。所化的代价是做一个面积较大的二极管。

图7.8(c)是一种低功耗FET逻辑(LPFL)。它是BFL和DCFL之间的折衷。所用的器件是开启电压接近于零的FET。逻辑门级和源跟随驱动级均采用电阻负载的DCFL形式。功耗比BFL低得多,但仍高于DCFL。由于开启电压低,管子导通比DCFL充分,因而速度比DCFL快得多。

图7.8(d)是E/D FL。象MOS电路一样,设法把D MESFET和EMESFET做在一起。这种电路虽然在工艺上有一定的复杂性,但电路形式变得十分简单,速度也比较快,单门延迟时间小于50ps。

GaAs作为超高速电路会受到某些因素的限制,主要是最大功耗和内连分布参量引起速度的衰退。BFL和SDFL主要受最大功耗的限制,一般被限制在1000门以内的集成度水平。DCFL可以达到比BFL、SDFL更高的集成度。而主要受内连线延迟的限制,连线太长,会失去高速的特点。在保持高速的前提下,限制集成度为几千门水平(不包括存储器)。随着技术的进步,GaAs高速电路的集成度和性能正在不断地提高。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助