电子技术论坛

信息来源: 时间:2022-5-13

GaAs组成高速数字电路的器件性能特征解析

组成高速数字电路的器件

由GaAs器件组成的高速数字系统的性能可以比用普通的硅器件的大大增强。它的单门延迟可达几十皮秒,功耗为几十微瓦。

组成GaAs数字集成电路的器件主要有如下三种:

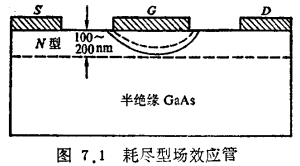

1、耗尽型Schottky势垒外延场效应管(D MESFET)

其工艺结构如图7.1所示。在半绝缘的高阻衬底上外延一层N型GaAs,其厚度为100~200nm。两边用欧姆结引出作为源漏,中间做成一个金属与半导体接触的Schottky结。由于金属与NGaAs的功函数不同,形成了一个耗尽载流子的势垒,这个势垒的宽度受栅金属电压的控制。当VGS=0时,耗尽层的宽度小于外延层的厚度,因此它是常通的耗尽管。当栅上加上足够大的负电压时,耗尽层的宽度达到外延层厚度,外延层被夹断。夹断电压一般控制在-2.5V左右。

这类由金属和半导体接触构成的栅控场效应管,简称为MESFET。

2、弱增强型MESFET(EMESFET)

将外延层减薄,使在零栅压下外延层就被夹断,由此形成增强型管。图7.2为它的结构剖面图。当栅上加正电压时,耗尽区缩小,管子开启。但是,能加的正电压受到严格的限制,不能大于Schottky势垒的高度,约为0.5V,否则会造成大的栅电流,这显然是不允许的。

因此,逻辑摆幅只能在0.5V以内,开启电压也只能设计在0.3~0.4V的范围内。因此减弱了电路的抗干扰能力。

与耗尽型MESFET相比,增强型MESFET由于导电外延层薄,管子跨导小,速度低,但有功耗低的优点。

E MESFET的存在使GaAs数字电路的设计变得简单,可模仿硅MOS电路的设计形式。

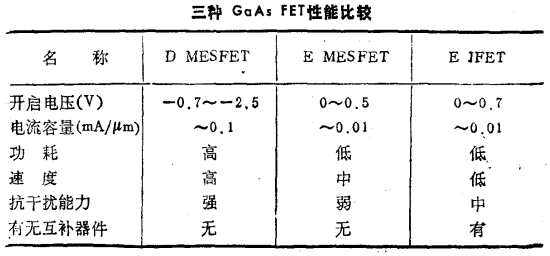

3、增强型结型场效应管(E JFET)

如图7.3所示,用离子注入P型区形成栅区pn结,代替Schottky结,组成JFET。外延层厚度为100~200nm,结深为50~100nm。零偏时结下的N区(外延层)被耗尽掉,因此是开启为正的增强型JFET。由于GaAs的pn结势垒比Schottky势垒高,约为1.2V左右,因此允许有比EMESFET高的逻辑电平摆幅和开启电压(约0.7V左右),它的抗干扰能力也随之增强。

JFET比MESFET的另一个重要优点是它可以构成互补器件,即P沟和N沟器件。由它们可以组成类似于CMOS形式的高速低功耗电路。而MESFET很难做成P沟器件,因为金属在P GaAs上做不出Schottky结。

由于pn结的侧壁栅电容很可观,JFET的速度明显低于相同条件下的MESFET。

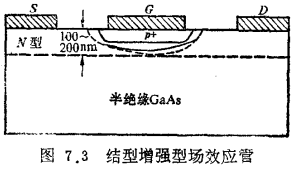

有关这三种GaAs器件的性能比较列于下表;

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助