电子技术论坛

信息来源: 时间:2022-5-11

通用阵列逻辑(GAL)EEPROM单元电路结构特征作用解析

可编程逻辑器件(PLD)就是可编程的PLA及PAL,PROM等。它们不是用掩膜编程,而是用电学方法编程。

近年来开发成功的通用阵列逻辑利用EEPROM作为单元组成PAL。它的优点是便于多次程序化,因而具有良好的可测性,这是由于器件出厂前可以通过多次编程对它的性能进行考验。

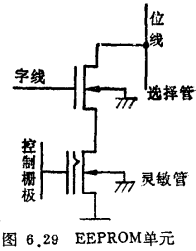

1、EEPROM单元

它由两管组成,如图6.29新示,一个是选择管,为普通的NMOS;另一个是灵敏管,为浮栅结构。EEPROM单元的写和擦是利用通过浮栅与漏区之间的超薄氧化层的隧道电流进行的。具体做法是用一个20V左右的脉冲,使电子向浮栅充电或将电子从浮栅上通过漏区拉出,以此使灵敏管处于常闭或常通状态,达到预定的编程。

EEPROM 单元除了编程和擦除速度快的优点外,还有浮栅电平保存时间长(100年以上)和擦写耐久性好(104次以上)等优良特性,深受用户欢迎。

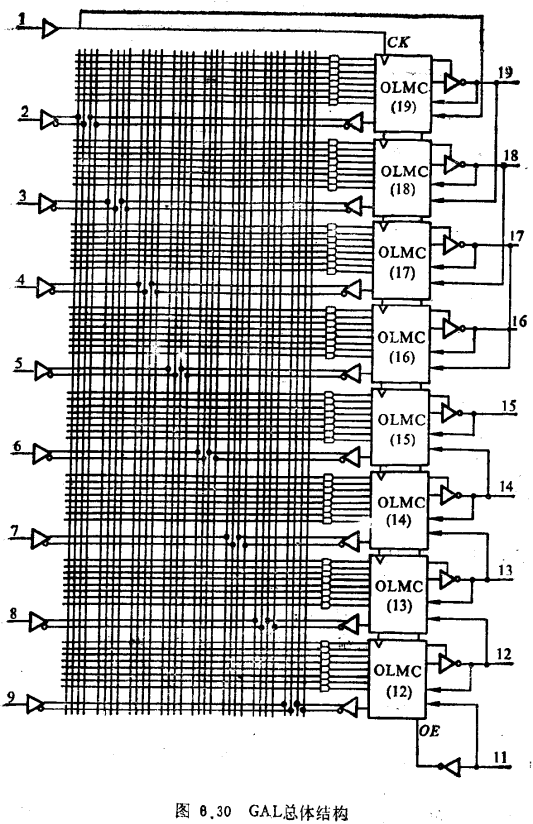

2、电路结构

图6.30是一种GAL的电路总体结构。中心阵列是一个64×32的PAL。AND矩阵用EEPROM组成,而8×8的OR门组采用固定端输入形式。每个输出端配上一个输出逻辑宏单元(OLMC),使其功能及灵活性大大加强。

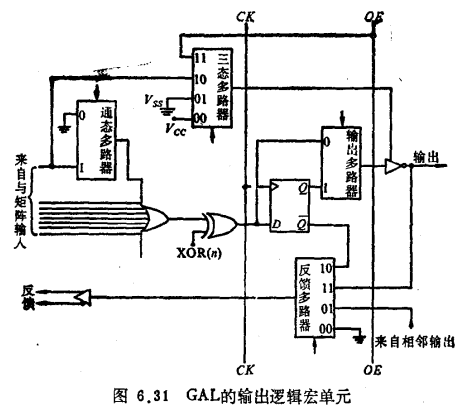

OLMC的电路结构如图6.31所示,包含有四个多路器、一个D触发器、一个XOR门、一个输出缓冲器(带三态控制)及连接AND矩阵的8输入或门。用电编程的方法来控制这些多路开关及XOR的状态,使GAL工作方式能够灵活应变,以满足各种应用的要求。

来自与矩阵的8个输入中的1个要经过一个通态多路器。这个多路器通过编程控制以决定这个输入作为正常的OR门输入或者通过三态多路器作为输出缓冲器的三态控制讯号。

OR门后面跟着的XOR门可以通过讯号XOR(n)控制OR门的输出要不要反相。这对简化乘积项是十分有用的。例如

共需9项相或,超过PAL的固定OR门的最多输入端数。这时可用转换律得:

仅需一个乘积项。再用XOR门把它反相过来得到O。为此,XOR门的编程控制讯号XOR(n)应为1。

仅需一个乘积项。再用XOR门把它反相过来得到O。为此,XOR门的编程控制讯号XOR(n)应为1。

通过控制输出多路开关决定是通过寄存器输出或是直接输出,以此分别构成时序逻辑或组合逻辑。

此外,三态多路器有四种选择:VCC为无控制直接输出,VSS(地)为阻止此OLMC输出,OE为由总输出讯号控制输出以及由一个来自与矩阵的输入端控制输出。反馈多路器也有四种选择。如图6.31所示,它可以接收相邻宏单元的输出讯号进行反馈。这些都是为适应GAL多种工作方式所必需的。

下面我们列出OLMC三种典型的输出结构形式:

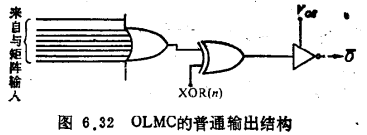

(1)普通组合输出结构

如图6.32所示。8个来自与矩阵的输入相“或”,再通过输出缓冲器反相输出 。这种结构十分简单,不包含寄存器,也没有反馈,因此是一种单向的组合逻辑。

。这种结构十分简单,不包含寄存器,也没有反馈,因此是一种单向的组合逻辑。

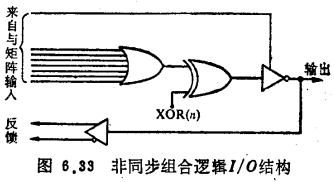

(2)非同步组合逻辑I/0结构

如图6.33所示,输出级由一个与项进行三态控制。输出讯号反馈回来作为与矩阵的输入项,但无时序控制,是一种双向(I/O)的组合逻辑。

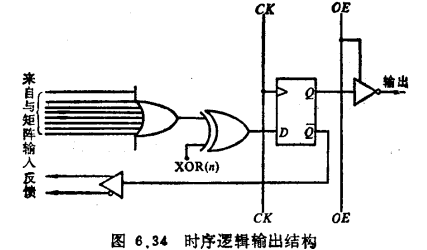

(3)时序逻辑输出结构

如图6.34所示,用一个D触发器作为寄存器,由一个时钟讯号CK所控制。它的反相输出 反馈到与矩阵作为输入的一部分,以控制下一个状态输出。它的输出缓冲器由讯号OE控制。

反馈到与矩阵作为输入的一部分,以控制下一个状态输出。它的输出缓冲器由讯号OE控制。

为了提高GAL的性能指标,除AND矩阵外均采用短沟CMOS电路。当沟道长度为2μm时,它的总延迟时间小于16ns;当沟道长度降到1μm时,总延迟时间减少至10ns以下。这样的速度已经达到和优于TTL的速度,因而GAL能代替由多个中、小规模TTL所组成的印刷电路板,这对整机小型化起着重要的作用。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助