电子技术论坛

信息来源: 时间:2022-5-10

时序程序逻辑阵列和流程图电路特性说明

时序程序逻辑阵列

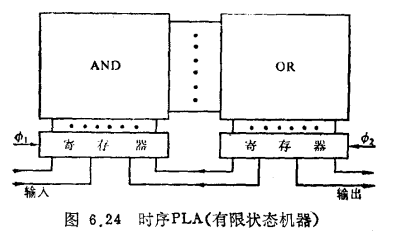

一般没有寄存器的无时序PLA只能完成组合逻辑功能。把PLA用于控制就需要有时序控制的状态寄存器及从输出到输入的反馈。下一个输出状态不仅是输入的函数,而且是当前状态的函数。这种时序PLA的结构如图6.24所示,组成所谓“有限状态机”。图6.24中的AND ROM和OR ROM各有一个不同时序的采样保持寄存器。它们分别由两相时钟控制,各延迟半个周期,其电路十分简单,仅用时钟控制的MOS单管组成。

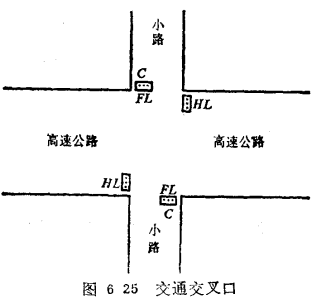

下面举一例说明时序PLA控制器的设计方法。图6.25表示一条高速公路与一条乡间小路的交又路口。为此要求设计一个合理的时序PLA交通控制器。高速公路上来往车辆很多,为了保路证车辆畅通,拟定了如下的交通控制方案:在小路的每侧路口各设置一个车辆探测器C,当小路上没有车辆等待时,C=0,始终保持大路通行,高速公路方向开绿灯,用HG表示这个状态。当小路的路口有车辆等待时,C=1,提出小路放行的要求。但对小路的放行不同于大路,有一定的时间限制。大路发出放行讯号的时间不得短于时间T,而一次中断时间也不得大于T。这样,即使小路提出放行要求(C=1),但也必须等待大路放行时间T之后才能允许小路放行。另一方面,大路中断时间不能超过T,即小路的放行时间不得超过T。小路放行时的状态用FG来表示。由HG→FG及FG→HG有一个短时间的过渡状态HY和FY,维持时间为T’,Y表示黄灯。

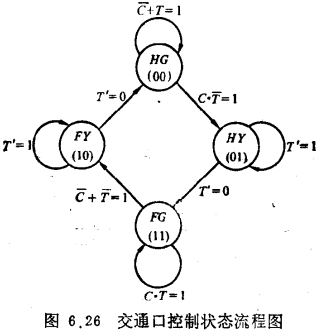

根据上述的控制方案,可得如图6.26所示的状态流程图,这是设计时序PLA的第一步。因为只有四种状态,因此可用两位二进制码A、B来表示它们:00表示HG,01表示HY,11表示FG,10表示FY。如果原来状态是HG,只要小路上没有车辆或时间T尚未终止,即 ,HG状态继续保持。当小路有车辆等待,并且大路通行的时间已达到了T后,即

,HG状态继续保持。当小路有车辆等待,并且大路通行的时间已达到了T后,即 ,则由HG→HY。HY保持一个短时间T’,即T’=1期间。然后,当T’结束,即T’=0时,由HY→FG。FG保持的条件应是C·T=1,一旦当C·T=0时,则FG→FY。FY也保持一个短时间T’,在T’=0时由FY回到HG。时间T和T’由两个定时电路所控制,当状态改变时有讯号S启动定时器,开始计时。交通管理最终要控制大路和小路的红、黄、绿三个讯号灯,可用两位二进位码进行控制,它们是HL1、HL0和FL1、FL0。00表示绿灯,01表示黄灯,10表示红灯。

,则由HG→HY。HY保持一个短时间T’,即T’=1期间。然后,当T’结束,即T’=0时,由HY→FG。FG保持的条件应是C·T=1,一旦当C·T=0时,则FG→FY。FY也保持一个短时间T’,在T’=0时由FY回到HG。时间T和T’由两个定时电路所控制,当状态改变时有讯号S启动定时器,开始计时。交通管理最终要控制大路和小路的红、黄、绿三个讯号灯,可用两位二进位码进行控制,它们是HL1、HL0和FL1、FL0。00表示绿灯,01表示黄灯,10表示红灯。

在流程图的基础上,设计的第二步是列出输入和输出的逻辑关系表。由于下一个输出状态与本次状态有关,因此表示本状态的二进制码An、Bn应反馈到输入端。当状态发生变化时,应输出定时器T及T’的起动讯号S。由上面的分析可得到如下输入和输出逻辑关系:

按上表可以组成如图6.27的PLA。输入和输出各放一个分别由时钟ф1和ф2控制的传输门,以实现寄存器的反馈。该PLA中的ROM用码点来表示。定时器外接,不属于PLA之内。

总结起来,设计一个实用的PLA一般分成如下三步,

(1)画出用户要求的状态流程图;

(2)列出输入和输出逻辑关系表;

(3)构成PLA电路及掩膜。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助