电子技术论坛

信息来源: 时间:2022-5-9

多单元门阵列局部平面图及其技术特点解析

多单元门阵列

标准单元法的缺点是不能预工艺,设计和制作周期较长,而门阵列的缺点在于单元单一,设计的灵活性和硅片利用率低。把两者结合起来进行适当的折衷,开发出一种多单元门阵列技术。

它的主要特点如下:

1、预工艺到多晶硅光刻:

2、利用单元库支持;

3、单元间用不开启的MOS管隔离。

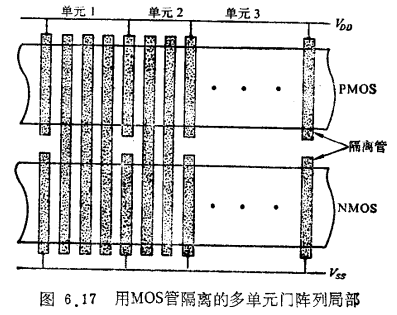

图6.17画出用MOS管隔离的多单元门阵列的平面图。由于不采用场氧化隔离,用多晶硅来确定单元之间的边界,ASIC工艺起步于多晶硅光刻,于是约有一半工艺可以通过预工艺实现。用户化的定制掩膜只需四块,即多晶硅光刻、阱接触孔、金属接触孔和金属布线。

通过布局计算,确定布局后就安排多晶硅隔离条,进行单元区划分。以双阱型CMOS为例,N阱中P扩散区的多晶硅隔离条接电源VDD;P阱中N扩散区的多晶硅隔离条接地Vss。布局后的布线方法与一般的标准单元法相同,但是它有门阵列的弊病,即芯片面积是预先固定的,不可能有100%的面积利用率。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助