电子技术论坛

信息来源: 时间:2022-5-6

标准单元法基本原理及其设计流程图分析

标准单元基本原理

由于门阵列的基本单元单一,不可能使得ASIC的设计在硅片利用率、速度和功耗等方面的性能最佳化。标准单元法正是为了克服门阵列的以上缺点而发展起来的。

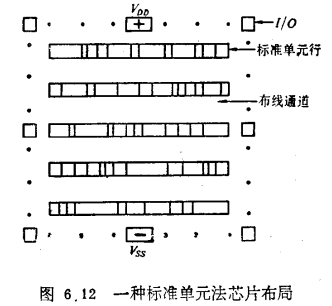

它的基本设计思想是用人工设计好各种成熟的、优化的、版图等高的单元电路,把它们存储在一个单元数据库中。根据用户的要求,把电路分成各种单元的连接组合。通过调用单元库中的这些单元,以适当的方式将它们排成几行,使芯片成长方形,行间留出足够的空隙作为单元行间的连线通道。图6.12为标准单元法芯片布局的一种典型结构形式。

利用CAD工具,根据已有的布局、布线算法,可以自动布出用户所要求的ASIC。这种布局布线法与传统用于自动设计印刷电路板的方法大致相同。它比门阵列的版图紧凑,电路优值好。由此带来的麻烦是工艺不能预制,需要有整套的掩膜版,因此制作的成本高、周期长,不如门阵列方便。

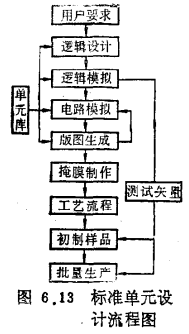

标准单元法的制作流程与门阵列基本类似,但单元库的支持起着关键作用。它不但支持版图设计,同时也支持逻辑和电路设计。其制作的流程框图如图6.13。

这里需要说明如下几点:

1、单元库中单元的形式和设计并不标准化,各公司都有自己的单元库,并且相互保密。

2、电路模拟与版图设计有迭代关系。必须在版图确定以后,从中提取分布参量,再进行模拟,才能最终得到可靠的电路模拟结果。

3、测试矢量的生成是由逻辑和失效模拟的结果所产生的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助