电子技术论坛

信息来源: 时间:2022-5-6

宏单元布线图及其逻辑图工作原理特征解析

宏单元

LSI和VLSI门阵列的全局自动布线往往要求很大的计算工作量。CPU的计算时间与器件包含的门数平方成正比关系。为此,先在较小的面积内局部布线,连成一定功能的逻辑块。它的规模可以比上述的基本逻辑单元大,当然也包括它们,这些功能逻辑块叫作宏单元。

宏单元可以有上百种之多。把已设计好的一些宏单元存储在一个数据库中,称为宏单元库。在此基础上,用户通过布线把各宏单元连成用户所要求的电路。这实际上也是分级布线,可使布线的计算工作量小得多。

组成宏单元库以后,可由用户用宏单元进行门阵列电路设计。

具体做法为:用户用已定义的宏单元逻辑块符号表示全电路的逻辑图,由此逻辑图作为输入,运行自动布局布线程序,以形成用户要求的电路。由于宏单元库的建立,门阵列除了布线还需要布局,即要把指定的宏单元放到最合理的位置。所谓合理布局就是便于布线。这种用宏单元进行门阵列电路的设计方法与第二节要介绍的标准单元法相类似。

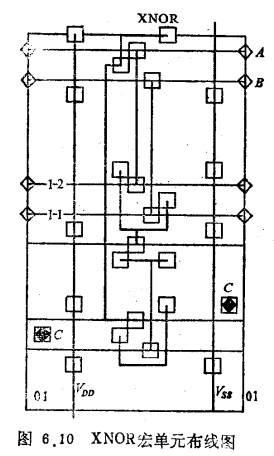

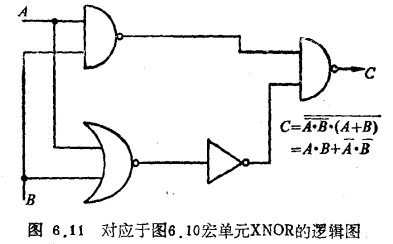

图6.10和图6.11为一个宏单元的实例,采用图6.7所示的单元。这个宏单元是一个XNOR门,包括了三个门阵列基本单元,通过单元内部的布线形成此宏单元。图6.10和图6.11分别是它的布线图和逻辑图。

宏单元法用于一些重复性的规则电路则更为方便。例如,多位移位寄存器、加法器及计数器,只要以其中一位作为一个宏单元,将数个相同的宏单元依次相连就可以组成这些电路。

有关门阵列自动布局布线的算法是一个比较复杂的问题,我们不可能把所有可能的布线路径进行比较和选择,因为计算工作量太大。为此,一般采用两种较方便的基本布线方法,即直接布线算法和迷宫找路布线算法。

直接布线算法快而简单,一般可以完成总布线的85%左右。它基于最直接简单的原理:两个需要连接的结点用一条直观最短的通道线把它们连在一起。但是,不可能100%的连接都能用这种方法,约剩下15%左右的连接线只能通过弯道连通。一般采用迷宫找路算法,找出可能的各种路径,并选择其中最短的一条。

上述布线算法的考虑并不全面,因为它还没有从电路性能上来分析。一般各种用户电路中总有一些关键的连线,称为要害路径。从电路性能上要求它们的延迟时间尽量短,否则会妨碍整个电路的工作速度。例如一个D型计数触发器电路中经过门数最多的一路连线的延迟决定最高计数速度,因此对这一路的诸连线必须给予特殊的考虑,也就是对它们优先进行最短布线,使它们的延迟最小。在此前提下再进行其他连线路径的布线。当然,这样做的结果必然会使门阵列的布通率有所降低,但这是必要的牺牲。

最后还要指出一点:不论是宏单元分级布线,还是要害路径优先布线,制作掩膜数并不增加,因为它们的数据文件在形成布线掩膜文件时都是融合在一起的。单层金属布线还是一次掩膜版;双层金属布线还是三次掩膜版。因此,门阵列是目前最简便的ASIC结构形式,在ASIC产品中占有最大的比例。它的最大缺点是芯片面积较大,而积利用率较低,不能达到设计最优化。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助