电子技术论坛

信息来源: 时间:2022-4-27

指令译码器ID的设计原理及其特征分析

指令译码器ID的设计

我们以一种8位微处理器为例,具体说明ID的设计方法。一般来说,ID采用简单的PLA结构较为方便。

为了便于分析,将8位机器指令操作码用ABCDEFGH来表示,A为最高位,H为最低位。

我们设计指令译码有两种不同的入口特征:一种是直接入口,即指令操作码本身就是其微程序入口;另一种是共同入口,即一些类似的指令具有共同的微程序入口,当微程序转到↑(按操作码转移)时,就可以相互区分。

为了设计ID,首先要列出这两种入口的特征方程,然后组成PLA形式的电路。

1、直接入口指令

根据某个实例,把所有直接入口的指令分成5部分: ,20及30。

,20及30。

令这些指令组的各自特征为W1,W2,W3,W4和W5。

共有16条指令,其特征:

共有16条指令,其特征:

10→17共有7条指令,其特征:

也有16条指令,其特征:

也有16条指令,其特征:

同样可得:

20对应

30对应

直接入口的译码方程为:

2、共同入口指令

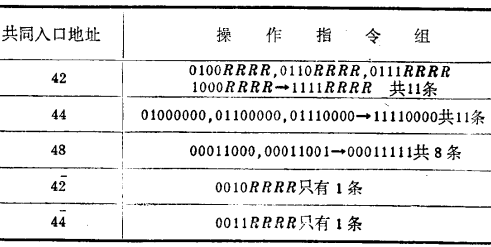

它与上述的译码方法略有不同,先列出有哪些共同入口地址及各自对应的操作指令组,如下表所示。

表中低四位RRRR代表了寄存器0001至1111共15个单元的地址,其特征为:

为了求出共同入口的特征方程,用卡诺图可得:

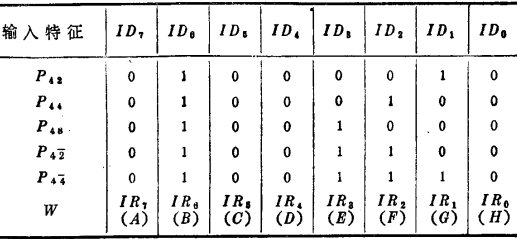

它们与IDi输出的联系见下表。

注意到ID0,ID4,ID5,和ID7,在共同入口中没有“1”输出项,故它们只决定于直接入口项。

总的ID译码方程如下:

把Pxx及W代入上式,就可以得到IDi的ABCDEFGH“与或”方程,由此很容易组成标准的PLA结构,由它完成指令译码的功能。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助