电子技术论坛

信息来源: 时间:2022-4-25

运算电路乘法器的单元电路具有三种形式解析

单元电路

高速乘法器一般采用短沟CMOS电路形式,具有高速、低功耗的优点。

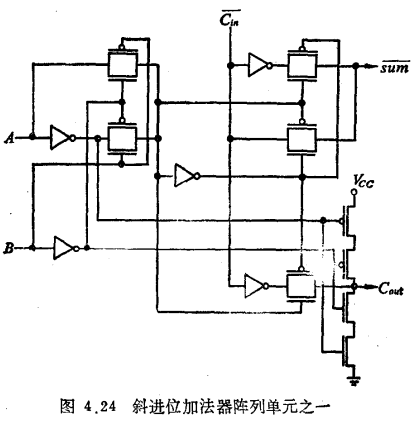

1、斜进位加法器(CSA)

为了加快连续加法的速度,减少门延迟级数,采用正码和反码输出的两种CSA,在阵列中交叉使用。图4.24为这种CSA的单元电路。该电路设计较为合理。从 到

到 只需经过一级反相器和一级传输门。

只需经过一级反相器和一级传输门。

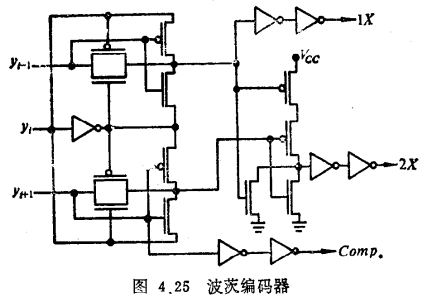

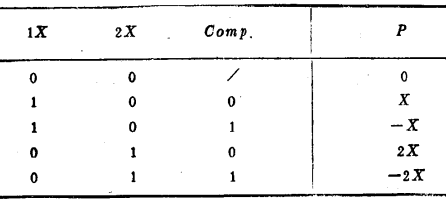

2、波茨编码器

采用类似的CMOS电路结构,由yi+1、yi及yi-1(为考察位)输入,产生3个控制讯号1X、2X和Complement,用加法阵列得到0、±X及±2X,实际上Comp。讯号是用以选择被乘数是正码或反码。图4.25为波茨编码电路,它的控制讯号与所产生部分的关系如下页表所示:

2X实际上就是X 左移一位。

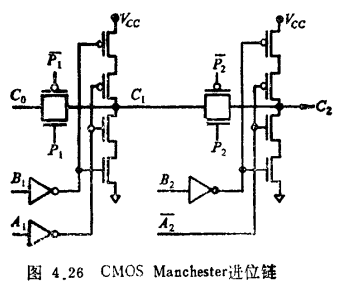

3、最终加法器

如图4.26所示的Manchester进位链,与图4.9的电路相一致。为了加快加法速度,象微机电路一样,采用超前进位的方法,超前的位数可变,一般是4位至6位。

流水线寄存器采用简单的主从D型触发器形式,由专门的时钟进行控制。

乘法器可以单独使用,也可以作为数字处理系统中的一个重要的运算部件,与其它运算电路集成在一起,组成功能更强的运算电路,如DSP和协处理器(Coprocessor)等。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助