电子技术论坛

信息来源: 时间:2022-4-24

运算电路乘法器结构框图及其加法阵列结构分析

乘法器结构

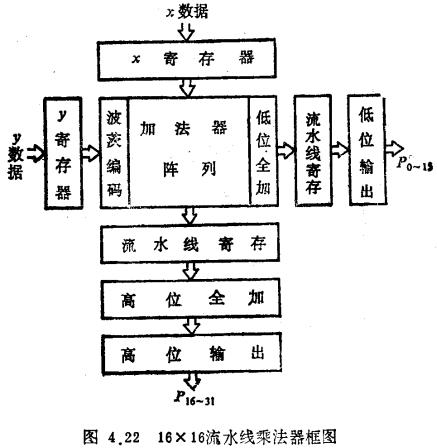

一个16位乘16位的流水线乘法器的结构框图如图4.22所示。它的核心是由部分积诸项组成的加法器阵列,有N/2行,2N列,最高位为符号位。此外,还有x、y地址缓冲寄存器、波茨编码器、高16位和低16位各自的总加器、流水线寄存器及输出缓冲寄存器。

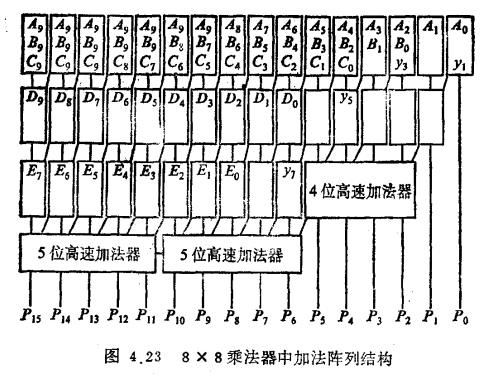

它的工作过程如下:16位的x、y输入后,x经y的波茨编码,产生8项部分积,其中的每一项都可能是0、±X、±2X这5种之一,并输入到相应的加法器,进行加法运算。在乘法器中,这些部分积相加均采用斜进位加法器(CSA)来实现。以前述的加法表为依据,8位乘法器的加法阵列结构如图4.23所示。斜进位加法器的优点在于可以大大提高加法速度。如图4.23所示,A、B、C三行部分积首先相加,它们不是一级级向高位进位,而是各自向下一个加法的高一位进位,由此可以省去进位的等待时间。第二行全加器的输入是本行D及对应上行同位加法的结果,还有上行低一位全加的进位。以此类推到下面各行的加法器。最后一次出终值的加法不能用CSA。为了提高加法速度采用前述的超前快速进位链的方案。

为了加快连续乘法的速度,象高速微处理器电路一样,也可以采用流水线工作方式。具体方法有多种,可以单级,也可以多级。图4.22是单级流水线结构,在高16位和低16位的最终加法器前后加上流水线寄存器,一旦乘法运算的中间数据被寄存,新的乘数和被乘数就可以输入运算。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助