电子技术论坛

信息来源: 时间:2022-4-14

专用RAM的结构框图和工作原理方式解析

将RAM和逻辑电路结合起来组成专用RAM(又称为ASIC RAM),使RAM的应用更为方便有效。

ASIC RAM近期发展较快,它以应用为对象,设计适合于使用的多种多样的专用RAM。视频显示RAM就是其中重要的一种,已经广泛用于显示整机。本节将以它为例,说明ASIC RAM的结构和工作方式。

对显示用RAM(V RAM)的基本要求是:必须能从图形控制器接收讯息,并在显示屏上显示RAM所存的内容。当用户要求的分辨率提高,就必须提高显示点速率,单靠普通的DRAM按地址一位位读出的速度肯定不能满足要求。

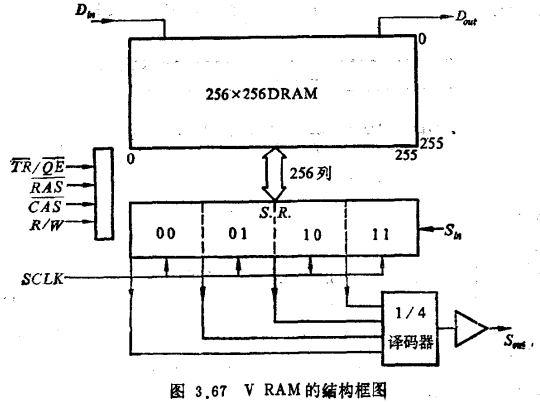

V RAM结构框图如图3.67所示。它包括一个256×256的64K DRAM、256位移位寄存器及有关控制电路。在一个读周期内把选中行的所有列的数据都传输到移位寄存器,再由较高的时钟频率(如25MHz)逐点输出到显示器。这样,每次输出还是一位,但是输出数据的速率大大加快。

RAM与移位寄存器(S.R.)之间的联系由讯号 来控制。当

来控制。当 为高电平时,它们之间失联,RAM可以正常按地址取数。相反,当讯号

为高电平时,它们之间失联,RAM可以正常按地址取数。相反,当讯号 为低电平时,可以把选中行的数据传到S.R.或者把S.R.中的数据写到RAM的一行中去。SCLK是控制S.R.的主时钟,可使S.R.中的数据逐级移位并输出到Sout缓冲器。

为低电平时,可以把选中行的数据传到S.R.或者把S.R.中的数据写到RAM的一行中去。SCLK是控制S.R.的主时钟,可使S.R.中的数据逐级移位并输出到Sout缓冲器。

此外,将256位S.R.分成4段,由A6、A7两位地址码进行选择,使移位输出总位数可变为64位、128位、192位和256位。S.R.可以从Sin接受外讯号,并可向RAM同时写入一行,由此可缩短向RAM装载讯号码的时间。

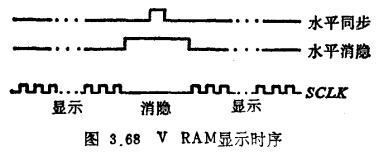

显示时间与向S.R.传输数据时间之间的配合是比较简单的,可参见图3.68。由一个水平同步讯号作为一次水平扫描的触发,由一连串时钟脉冲使S.R.中的数据输出,输出速度越高,显示分辨越高,因为一次扫描可以显示更多的点(数据)。利用回扫消隐的时间足以完成RAM的另一行数据向S.R.传输(装载)。如果行地址顺次变化就可以完成整幅图形的显示。

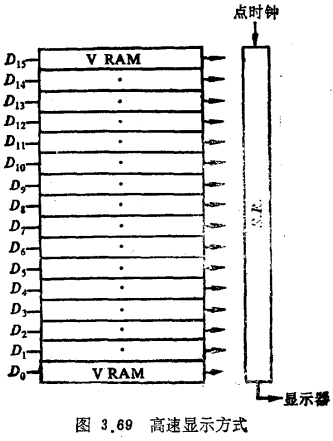

为了加速显示速度,可以采用图3.69所示的多个V RAM平行工作方式。如用16个V RAM的输出数据平行送入一个更高速的移位寄存器,即一次由16个V RAM装载16个数据,再由更高频率的时钟驱动它输出到显示器。

这种将RAM与适当的逻辑电路相结合的ASIC RAM,由于其功能和性能较简单的RAM有很大的提高,已成为当前RAM发展中的重要方向之一。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助