电子技术论坛

信息来源: 时间:2022-4-13

解析容错技术结构电路及读写过程采取措施技术

容错技术

冗余技术对纠正单元的硬失效是很有效的。随着集成度提高,单元尺寸缩小,α软失效又成了重要矛盾,而容错技术可以纠正α软失效。

容错技术的要点是在正常数据位以外加上几位校正码,校正位与数据位之间必须符合一定的编码规律。如果数据位读出发生错误,校正位也会随之变化,从新、老校正位的差别可以检出数据位的错误,甚至可以纠正错误。

熟知的奇偶校正只有一位校正位,可使数据和校正位中的“1”数目为奇或偶,如果有一位出错,将会改变它们的奇偶性,由此可以判断数据是否出错。这种方法只能检出一位错误,但无纠错功能,不符合RAM容错技术的要求。

用汉明码作为校正码与数据码混编在一起,可以实现检1、纠1功能,即能检出1位错误,并将它纠正。

对M位数据码,要求K位校正码,可以证明最小的K与M有如下的关系:

以M=16为例,有K=5,两者混编在一起总共为21位。

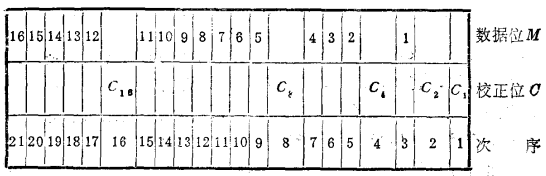

数据码和校正码混合编排次序如下:

其中C1、C2、C4、C8和C16为汉明校正码,它与数据位的关系和编法如下:

利用上述的编排,用新、老校正码的“异或”,产生5位的特征字S。如果S=0,则没有错误;如果S≠0,并设只有一位数据出错,那末S就标志出错位的位置,以编排次序为标志。

这里我们不用编码原理来证明上述的结果,只用一个实例来证实。

原数据为16位,0101 0000 0011 1001,读出只错一位为0101 0000 0011  。用上面公式计算原数据的汉明码C16C8C4C2C1为11110,错数据的汉明码为11001,由此求得特征字S为:

。用上面公式计算原数据的汉明码C16C8C4C2C1为11110,错数据的汉明码为11001,由此求得特征字S为:

特征字是5位二进制数。由上述可知,混编码的第7位有错。由编排表查得数据位的第4位出错,确与实际情况相符。

如果我们以E=M/(M+K)表示纠错效率,由前述的权明码位数与数据位数的关系可知,数据位M越少,纠错效率越低。一般M为20位左右较为合理,这时纠错效率较高。如果M很大,虽然E可更大一些,但效果不好,因为汉明码只能纠错一位,如M很大,·出错多于一位的概率大大增加,使它无法纠错。

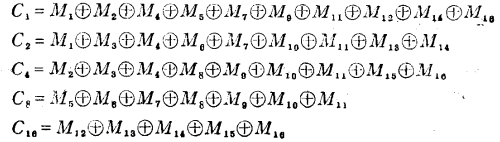

修正汉明码可以检出2位错误,纠年1位错误,它比普通汉明码的位数要多。可以证明,修正汉明码的位数及与M的关系为:

下页表列出汉明码和修正汉明码位数与数据位数M的关系。

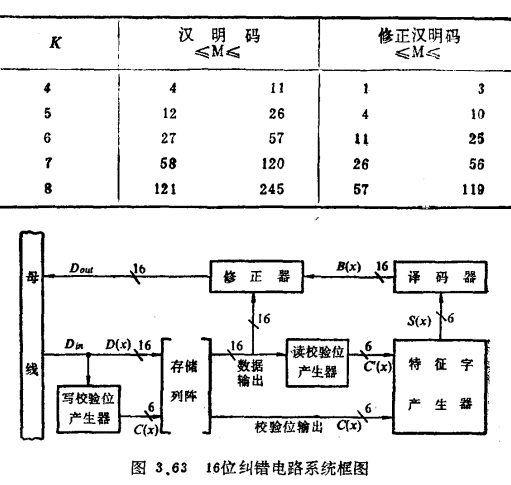

图3.63为用修正汉明码进行错误检测纠正(ECC)16位数据电路系统框图。除了本征RAM(包括纠错单元),还有一些附加电路,即校正码产生器(读、写各1个)、特征字产生器、译码器及纠错电路。图中M=16,K=6。由写入和读出的16位数据分别产生两组6位修正汉明码,再由它们产生6位特征字,经译码后产生16个B讯号,分别控制16个纠错电路。

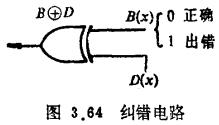

纠错电路实际上也是一个简单的“异或”门组,如图3.64所示。如果B(ⅹ)=0,Dout=D(ⅹ),即不纠错;如果B(ⅹ)=1, ,即对错位进行纠正。译码后的B(ⅹ)中至多只有1个是“1”,它指示错位的位置。

,即对错位进行纠正。译码后的B(ⅹ)中至多只有1个是“1”,它指示错位的位置。

由此可知,这种纠错方法对硬、软失效都能有效的纠正。但是,它的电路比较复杂,芯片面积增加较多,因此在规模不是很大、软失效矛盾不是十分突出的RAM中不宜采用。

一种在片ECC的方法比较适用于VLSI RAM,它是一种双向奇偶校正的方法,电路较汉明码法要简单一些。

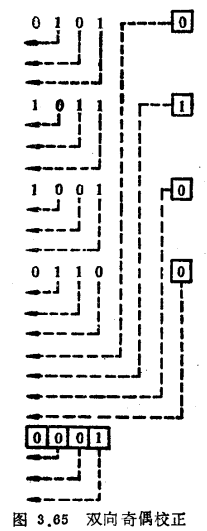

为了便于说明问题,我们以4×4的单元矩阵为例,在水平方向和垂直方向各加上4个奇偶校正码,图3.65中用的是偶校正。如果有一位数据出错,它所在行、列的校正码都会变化,由它们定出错位的位置,予以纠正。实验及计算表明,采用这种方法后α软失效率可以下降106倍之多。

如图3.65所见,这种方法对整个矩阵只能进行检1纠1。对于大的单元矩阵只纠正一个错误显然是不够的,因此要采取措施。图3.65上的16个单元可以排成矩形,也可以排在一条字线上,如图上虚线箭头所示。再加8位水平和垂直奇偶校正码。这样可以对每一条字线纠一个错,以此提高纠错能力。如果一条字线上位数很多,那末就将它们分成若干组。

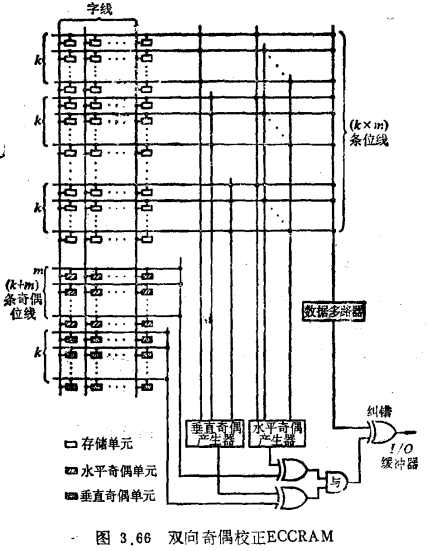

图3.66为一个完整的双向奇偶性纠错电路系统,它以一条字线作为一个单元矩阵,共有 个单元,应加上

个单元,应加上 个奇偶校正单元。我们把这些在一条字线上的单元看成

个奇偶校正单元。我们把这些在一条字线上的单元看成 单元矩阵,即m个垂直校正码,

单元矩阵,即m个垂直校正码, 个水平校正码。根据校正码的变化,决定该矩阵中出错位的位置,并设法加以纠正。

个水平校正码。根据校正码的变化,决定该矩阵中出错位的位置,并设法加以纠正。

读出 位数据,产生新的一组

位数据,产生新的一组 个校正位,它们与原来写入的校正位单元逐个进行比较,比较方法类似于汉明码容错电路,再对比较结果进行译码。每一个读出单元数据应对应于水平和垂直各一个校正位,如果都出错,表明该单元数据出错,需要纠正。纠错电路也是“异或”门,水平和垂直校正码的比较也由两个“异或”门来完成。如都出错,经“与”门向纠错电路(XOR)输入“1”,结果

个校正位,它们与原来写入的校正位单元逐个进行比较,比较方法类似于汉明码容错电路,再对比较结果进行译码。每一个读出单元数据应对应于水平和垂直各一个校正位,如果都出错,表明该单元数据出错,需要纠正。纠错电路也是“异或”门,水平和垂直校正码的比较也由两个“异或”门来完成。如都出错,经“与”门向纠错电路(XOR)输入“1”,结果 。如果有一位校正位不出错,“与”门向纠错XOR输入“0”,结果Dout=D,不需要纠错。

。如果有一位校正位不出错,“与”门向纠错XOR输入“0”,结果Dout=D,不需要纠错。

容错技术比冗余技术的电路复杂。由于读出数据要多经过一些门,因此取数时间变长。另外,芯片面积的增加也较冗余法多。它的主要优点是可以纠正软失效。目前,从工艺上来降低软失效率的工作也有不少进展,因此至今容错RAM芯片还未商品化。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助