电子技术论坛

信息来源: 时间:2022-4-12

解析冗余容错技术的成品率与缺陷的关系及采取措施

成品率与缺陷的关系

随着RAM集成度的提高,缺陷造成成品率下降成为了一个重要的矛盾。

如果一个大圆硅片上有N个芯片,片上有n个点缺陷。先假设这些缺陷是随机分布的。根据统计理论,芯片中有K个缺陷的几率:

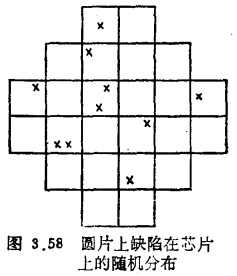

K其中 ,为单位芯片占有的平均缺陷数。图3.58是缺陷在大圆片各芯片上随机分布的实例之一。

,为单位芯片占有的平均缺陷数。图3.58是缺陷在大圆片各芯片上随机分布的实例之一。

令Do为缺陷密度,A为单个芯片的面积,Y为成品率,则应有:

显见,如果工艺水平保持不变,即Do不变。随着集成度和芯片面积的增加,成品率指数下降,上的随机分布问题是很严重的。

当然,以上分析中假设缺陷在硅片上随机分布,因而对成品率的估计过于悲观。实际上工艺缺陷常常是在局部地区团聚,由它们损害的芯片数比上述的计算结果少得多。但是,不管如何计算,随着芯片面积A和集成容量的增加,成品率总是要大幅度下降的。

从工艺方面采取措施,可以有效降低缺陷密度Do,至今已经取得了重大的进步,但是不可能使硅片上完全没有缺陷。有幸的是RAM是一种规则结构电路,各单元完全相同。因而可以设法多做一部分单元,用好单元去换掉一些有缺陷的坏单元,使成品率大幅度提高。冗余技术正是基于上述想法的一项有效措施,已普遍应用于高集成度的VLSIRAM中。

容错技术是将整机的容错方法用于片内。在正规存储单元以外加上一些编码单元,以此作为检错及纠错。随着RAM规模增大,已把容错电路做在片内,制成具有片内纠错功能的RAM,称为ECC技术。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助