电子技术论坛

信息来源: 时间:2022-4-11

VLSI SRAM地址变化探测法(ATD)电路及措施

这是降低SRAM维持功耗的另一有效措施。上述的SRAM在维持状态下不但有列电流功耗,还有其他外围电路的功耗,即使采用DWL技术,SRAM的维持功耗仍比DRAM的大得多。

为了大大降低维持功耗,可以模仿DRAM电路,采用时钟控制方式。例如用动态译码器,在维持状态下所有字线均为低电平(可见本章第四节中DRAM的译码电路),因此就不存在列电流。在这种工作方式下,维持功耗仅仅是单元列阵的功耗。前面已分析过,不论用高阻多晶负载,还是用CMOS互补负载,这项功耗都是很小的。但DRAM必须是同步工作方式,即选择时钟 及

及 具有固定的周期性,而SRAM可以是异步工作方式,只要地址发生变化,马上随时改变译码并取数。

具有固定的周期性,而SRAM可以是异步工作方式,只要地址发生变化,马上随时改变译码并取数。

为了使SRAM的外围电路动态化,又能异步工作,开发了ATD技术。一旦有地址变化就能触发片内一组时钟链,由它们控制完成从地址缓冲一直到数据读出。虽然片内外围电路全是动态工作方式,只有单元是静态的,但对用户来说,仍然与内部是真正的SRAM是完全一样的。

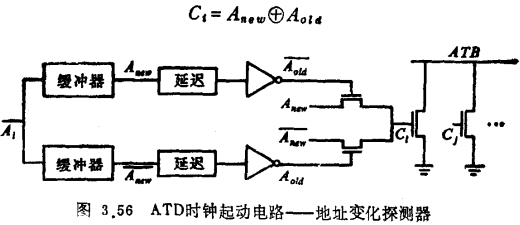

ATD的时钟起动电路如图3.56所示。在每个地址缓冲器上附加一个地址变化探测电路,它由延迟传输门和异或门所组成。由图可见

当地址变化时,Ci=1,否则Ci=0。

把各个Ci相“或非”,只要有一个地址变化,就会输出一个ATB负脉冲,因为Ci是一个正脉冲讯号。利用ATB去触发一组时钟链的产生,进行正常读出或写入。

采用上述技术也会带来一定的问题,即会使SRAM的速度降低,并增加电路的复杂性。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助