电子技术论坛

信息来源: 时间:2022-4-8

VLSI SRAM单元电路基本原理及其特征解析

静态随机存储器(SRAM)集成容量不及DRAM,一般为DRAM的1/4左右,这是因为它的单元电路较为复杂,占硅片面积大。但是它有两个优于DRAM的特点,即不需要刷新,使用方便和速度快。因此,在某些场合,例如高速缓冲存储器(Cache),必须使用SRAM。

一、VLSI SRAM单元电路

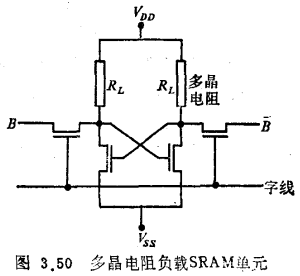

SRAM单元是由六个器件组成的触发器,触发器彼此的不同主要在于负载器件的形式,通常有耗尽管、多晶电阻、增强管及PMOS 互补管这四种负载。VLSI SRAM单元大部分是多晶硅高阻负载,其电路图如图3.50所示。它的优点是面积小和功耗低,这两点是衡量SRAM单元优值的最重要的指标。

单元功耗实际上决定于负载电阻的大小。多晶硅电阻RL由离子注入控制可达足够大的数值,一般在500MΩ左右,单元功耗Pc为:

这是一个很小的数,例如64K个单元,总功耗也只有3.2mW。

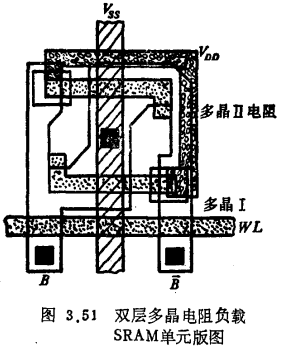

单元版图见图3.51,多晶电阻和多晶栅是由两层多晶分别形成的,电阻可以重叠在管上,不占面积,因此单元面积较小。

也有用PMOS作负载的CMOS单元,它可以有更低的单元静态功耗。如果把它用作由恒定小电源保持存储数据的不挥发存储器是十分合适的。

但是,CMOS单元比多晶电阻负载单元的面积要大得多,不宜普遍采用。

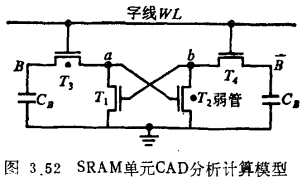

为了缩小单元面积,单元的门管和工作管在遵守工艺设计规则的前提条件下尺寸应尽可能小。但是门管和工作管的W/L之比应满足下述要求,即在读出时保持单元版图元的存储讯号稳定。

为此,下面将分析读出过程中单元存储讯号的变化

图3.52是进行分析的模型。在WL选上前,B和 均为高电平,并保持在CB上。当WL选上后,位线高电平通过门管T3、T4向a、b结点充电,T1、T2可能同时导通。如果在完全理想对称的情况下,原高电平结点a放电必然比原低电平结点b慢,由于正反馈作用的结果,T1截止、T2导通,存储讯号不变。实际上,类似DRAM S/R的分析,不对称性总是存在的。如果高电平端的门管T3是弱管(相对T4),低电平端的工作管T2是弱管(相对T1),那末就有可能a点放电比b点快,通过正反馈会引起单元触发器的翻转,存储讯号被破坏。

均为高电平,并保持在CB上。当WL选上后,位线高电平通过门管T3、T4向a、b结点充电,T1、T2可能同时导通。如果在完全理想对称的情况下,原高电平结点a放电必然比原低电平结点b慢,由于正反馈作用的结果,T1截止、T2导通,存储讯号不变。实际上,类似DRAM S/R的分析,不对称性总是存在的。如果高电平端的门管T3是弱管(相对T4),低电平端的工作管T2是弱管(相对T1),那末就有可能a点放电比b点快,通过正反馈会引起单元触发器的翻转,存储讯号被破坏。

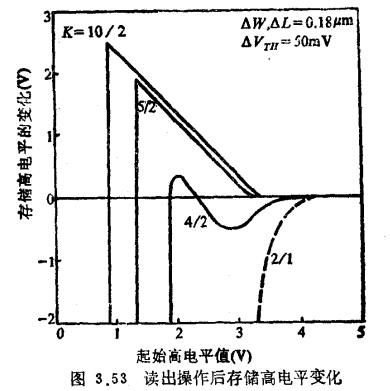

设K为工作管的W/L与门管的W/L之比,图3.53表示用计算机电路模拟方法计算出的不同的K值所对应的存储高电平的变化与起始高电平的关系。这样的计算是在下述合理的工艺容错下进行的,即ΔVTH=50mV,ΔW=ΔL=0.18μm。由计算结果可见,当K较大时,单元存储讯号比较稳定,起始高电平越大,存储高电平变化越小。如果以起始高电平为3.5V作为合理的下限,那末K为2/1、4/2都是不稳定的。大于5/2是稳定的。

由此看来,在上述的工艺误差条件下,选用K为5/2是比较合理的,实际上很多VLSI SRAM单元的设计基本上都采用了上述的计算结果。以1.5μm工艺为例,门管的W/L是3μm/1.5μm,工作管是7.5μm/1.5μm。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助