电子技术论坛

信息来源: 时间:2022-4-6

CMOS DRAM几种关键电路的设计解析(S/R放大器、行译码器等)

几种关键电路的设计

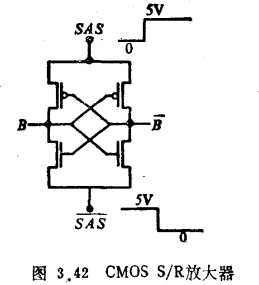

1、灵敏/恢复(S/R)放大器

用CMOS电路设计S/R SAS可以十分简单。图3.42就是用两对PMOS和NMOS管组成的S/R。当 上建立了小电平差后,SAS出现一个正脉冲,向

上建立了小电平差后,SAS出现一个正脉冲,向 充电,由交叉耦合的P管把它们的电平差放大,结果两个P管一开一关。开的一边达高电平VDD,关的一边为略高于Vss的低电平,后在

充电,由交叉耦合的P管把它们的电平差放大,结果两个P管一开一关。开的一边达高电平VDD,关的一边为略高于Vss的低电平,后在 点出现一个负脉冲,使它从高电平跳变为低电平。两个N管也是一开一关,开的一边原是低电平,被NMOS的导通而放电至Vss电平,另一边的高电平则被保持。

点出现一个负脉冲,使它从高电平跳变为低电平。两个N管也是一开一关,开的一边原是低电平,被NMOS的导通而放电至Vss电平,另一边的高电平则被保持。

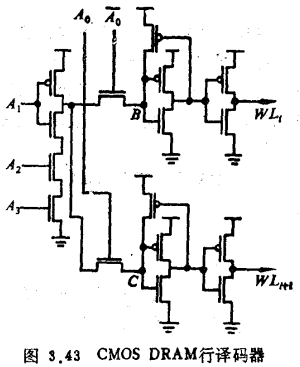

2、行译码器

由于地址数较多,如果采用正规的CMOS NOR或NAND进行译码,会有过多的管相串联,对提高电路速度和缩小芯片面积都十分不利。图3.43为一种不用多负载管的行译码电路。它是用于PMOS单元的CMOS DRAM。在不译码时A1为低电平, 均为高电平,字线WL均未被选中。当进行译码时,只有地址码

均为高电平,字线WL均未被选中。当进行译码时,只有地址码 都是高电平的情况才能译中。译中时,结点B或C等向Vss放电。由于只有一条字线被译选中,也就是只有一路有放电电流,因此该译码器的功耗是很低的。

都是高电平的情况才能译中。译中时,结点B或C等向Vss放电。由于只有一条字线被译选中,也就是只有一路有放电电流,因此该译码器的功耗是很低的。

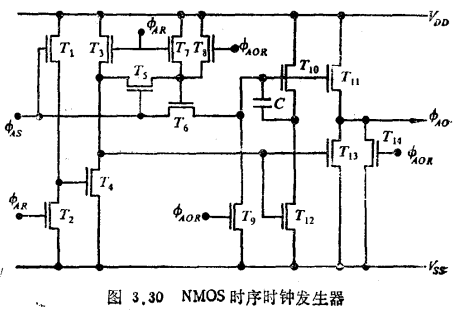

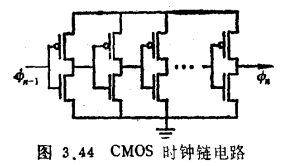

3、时钟发生器

它是DRAM不可缺少的电路。NMOS的时钟发生器电路如图3.30所示,电路比较复杂。这是因为预充和自举使电路复杂化。CMOS时钟发生器电路就可以简单得多,图3.44所示的电路由简单的多级反相器组成。延迟时间由反相器的级数及各级本身的延迟时间所决定,输出与输入的极性决定反相器级数的奇偶,因此十分便于设计。

总之,CMOS DRAM相对NMOS DRAM而言,电路大大简化,外围电路静态化,而且改进了各方面的性能,如速度、功耗和可靠性等,因此近期新设计的DRAM都采用CMOS工艺。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助