电子技术论坛

信息来源: 时间:2022-4-6

CMOS DRAM外围电路分类及基础电路分析

外围电路分为两类:

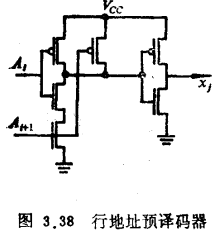

1、没有时序要求的电路采用最简单的全静态电路,例如行地址预译码器,见图3.38。

2、有时序要求的电路采用有时钟控制的静态电路。按照控制方式不同,又可分成三类:

(1)时钟控制驱动

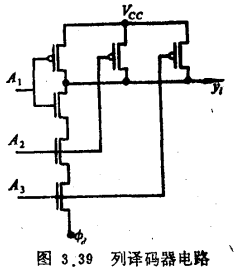

如图3.39所示的列译码器电路,要求在灵敏放大后开始工作,因此用时钟фd进行控制。平时фd为高电平,列译码器不工作。当灵敏放大后,фd为低电平,列译码按静态方式工作。

(2)时钟控制采样

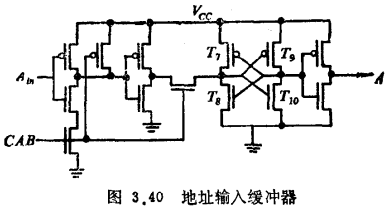

用时钟控制传输门的开闭来完成外来信息的采样,再由静态触发器来锁存采样的信息。图3.40所示的地址输入缓冲器是这类电路的一个典型例子。时钟CAB控制传输门采样输入地址Ain,T7~T10组成静态锁存器使电路静态化,避免A点成为靠电容存储电荷来保持电平的动态结点。

(3)时钟控制信号传输

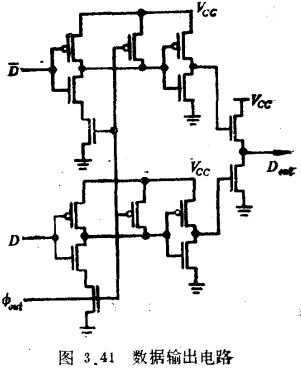

CMOS DRAM的外围电路大量采用这类电路,以便满足电路工作的时序要求。如图3.41所示的输出缓冲器,当输出控制信号фout为低电平时,Dout为高阻态输出,当фout为高电平时数据D被缓冲输出。

消除自举对短沟VLSI DRAM是很必要的,因为在自举结点上的高电平超过电源电压好几伏,会增强热电子效应和次开启漏电,这正是NMOS VLSI的难题。而CMOS无需自举,相对NMOS DRAM而言,是一重要优点。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助