电子技术论坛

信息来源: 时间:2022-4-2

详解CMOS DRAM单元剖面及电路基本组成分析

CMOS技术的发展为VLSI DRAM的设计提供了更好的工艺技术和电路形式,与NMOS相比,显示出多方面的优越性。从80年代中期开始,CMOS DRAM已经取代了NMOS DRAM,并已达到Mb级水平。

NMOS DRAM采用动态工作方式,利用时钟预充和电容自举达到低功耗及好的输出高电平,因此时钟多,电路复杂,影响工作速度。

CMOS电路具有无静态功耗、输出电平幅度大等优点。它的DRAM外围电路不需要预充和自举,可采用全静态电路和较简单的时序控制的静态电路形式,使电路结构大大简化,时钟数大大减少,工作速度更快、更可靠。

CMOS DRAM单元电路

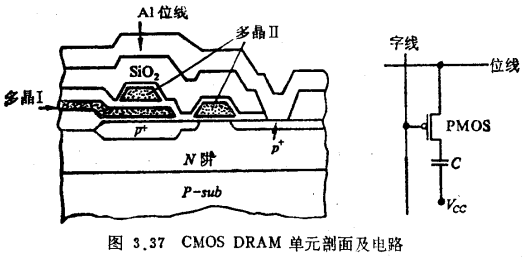

单元结构也是由一个门管和一个存储电容所组成。有些产品的单元是NMOS型,做在P型衬底上,与NMOS DRAM的单元相同。有些设计把单元做在N阱内,是PMOS型,它的单元剖面和相应电路如图3.37所示。这是以PMOS为门管的双层多晶。折叠金属位线单元。这种结构可以大大降低a软失效率,因为单元存储列阵做在一个大的N阱内,阱深为3~4μm,而a粒子的射程为20um左右,它所激发的电子空穴对大部分被N阱和P型衬底形成的pn结所吸收,达不到存储结点,由此N阱对存储点起着保护作用。实验表明,采用N阱保护可以使a软失效率下降儿百倍之多。但是这种结构中,单元存储电荷区下面是N阱,而不是接恒定电位的衬底,因此容易受到电源的干扰。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助