电子技术论坛

信息来源: 时间:2022-4-2

详解NMOS DRAM自衬偏发生器特性及其优势分析

目前的DRAM产品都是单+5V电源供电,在芯片内部有一个电压发生器,它的电压为-3V左右,作为加在衬底上的负偏压,以VBB表示。

VBB在片内的存在用户从外特性是看不到的,但对改善DRAM的性能有很多的好处:

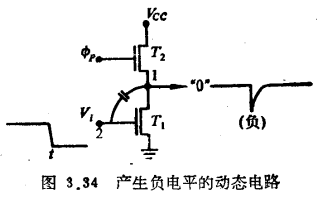

1、防止负过冲引起“1”单元失效

如图3.34所示的动态电路,原来结点2为高电平,输出结点1为低电平,T2处于关闭状态。当结点2在t时刻跳变到低电平时,结点1由于与2之间的电容耦合而造成负电平。1是T1、T2的源漏区,为n区,负过冲超过0.6V时,就会向衬底注入少子(电子),这是因为pn结处于正向导通。这些少子在衬底中扩散,很可能被附近处于pn反偏的存“1”单元所收集,结果使存“1”讯号丢失。负偏压加在衬底上以后,使pn结总是处于反向,可防止上述情况发生,大大提高单元存储的可靠性。

2、提高速度

pn结处于较大的反偏会使它的电容减小,而扩散区的分布电容正是影响电路取数时间的重要因素之一,它的减小有利于提高电路的速度。

3、增加单元电平的传输系数T

由前述可知,单元向位线的电平传输决定于CS/CB。衬偏存在使CB减小,必然使传输率T加大,有利于将单元讯号可靠地读出。

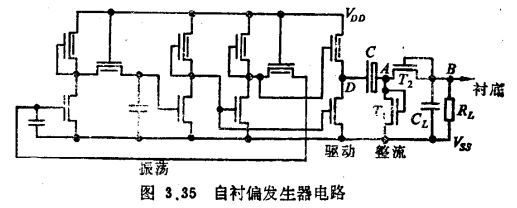

图3.35是一种典型的自衬偏发生器电路。它包括三部分:前面是三级反相器组成的环形振荡器,中间是驱动级,后面是起整流作用的电荷泵。振荡频率决定于两级等效的RC相移,一般设计成振荡频率为10MHz左右。经过驱动级得到近似为0到VDD(+5V)的脉冲振荡波形。由它供给电荷泵进行整流,结果在B点得到-3V左右的输出,B点与芯片的衬底相连,形成pn结反偏。

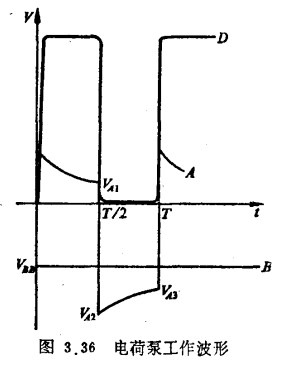

图3.36示出电荷泵工作的波形。当D点在正半周期间,通过电容C耦合,T1导通,A点的电平被放至VT1(T1管的开启电压);在负半周,通过C耦合,A点变为负电平,T2导通,VSS(0电平)通过RL及T2向A点充电,B点电平也是负的。

下面将计算一下泵电压VBB。在D点的振荡幅度VPP=5V,耦合到A的幅度如要比VPP小,这是因为A点有对地的pn结电容。A的幅度为aVPP,a为小于1的系数,它决定于C与pn结电容之间的分压,应有

其中Cpn为A点对Vss的pn结电容。

在正半周T1正向放电快,故有 。在负半周起始时在VA1点有一个幅度为aVPP的负跳变,VA2=VA1-aVPP是负电平。在这负半周内,Vss通过RL及T2向A点充电,A点电平略有提高。充电电流应近似为∣VBB∣/RL。以T表示振荡的周期,则有:

。在负半周起始时在VA1点有一个幅度为aVPP的负跳变,VA2=VA1-aVPP是负电平。在这负半周内,Vss通过RL及T2向A点充电,A点电平略有提高。充电电流应近似为∣VBB∣/RL。以T表示振荡的周期,则有:

另外,VBB应比 大

大 (T2管的开启电压),即

(T2管的开启电压),即

。将它们代入上面的公式,可计算出:

。将它们代入上面的公式,可计算出:

式中RL是衬底对Vss扩散区的反偏pn电阻,其值是很大的。由于振荡频率较高,T较小,因此在一般情况下T/(2RLC)项大大小于1,可以略去,那末应有:

为了估算VBB,提供如下的合理数据:a=0.8,VPP=5V,VT1=VT2=0.7V。由此可得:VBB=-2.6V。

如果需要提高衬偏发生器的负载能力,即R1较小,为了保持VBB不变,应该加大C和减小T,即提高环振频率。

在此要附加说明一点,自衬偏发生器不但对DRAM,而且对SRAM及其他类型NMOS VLSI都是需要的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助