电子技术论坛

信息来源: 时间:2022-4-1

NMOS DRAM输出级电路图分析及其基础作用

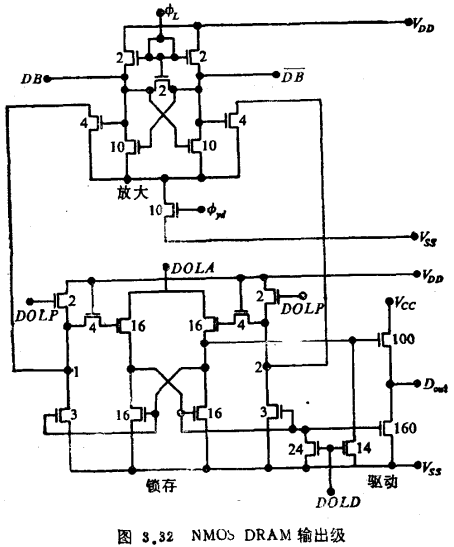

DRAM的输出级一般由输出放大器、输出锁存器和输出缓冲器三部分所组成。图3.32为一种典型电路。放大器与S/R基本类似,但管子W/L要大一些,以增加它的驱动能力。输出锁存器与地址输入缓冲器的第一级类似,DOLP时钟为结点1、2的高电平预充时钟。根据放大器的两端输出置1、2结点为一高一低电平,然后传入由触发器形式组成的数据锁存器,该数据将锁存至下一个周期。DOLD时钟由 触发,使缓冲输出的两管关闭,呈高阻态,作为起始的输出状态,以利提高速度。输出缓冲器是由两个W/L大的管子组成推挽电路,以能高速驱动片外较大的负载电容。

触发,使缓冲输出的两管关闭,呈高阻态,作为起始的输出状态,以利提高速度。输出缓冲器是由两个W/L大的管子组成推挽电路,以能高速驱动片外较大的负载电容。

写入数据的缓冲输入电路与地址缓冲输入电路基本相同,只是控制的时钟不同而已。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助