电子技术论坛

信息来源: 时间:2022-3-31

NMOS DRAM时序时钟发生器功能及电路图分析

在DRAM中有众多的时钟,它们是由外主时钟 和

和 (读写控制)触发形成的。由上述输入缓冲器的例子可以看出,它们要按一定时序配合各部分电路工作,组成时钟链。

(读写控制)触发形成的。由上述输入缓冲器的例子可以看出,它们要按一定时序配合各部分电路工作,组成时钟链。

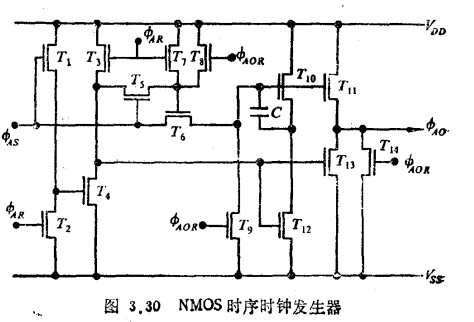

为了更具体说明问题,我们将以фAO发生器为典型实例进行分析。图3.30就是它的电路图。一个时钟发生器除了要求时序配合外,还要求输出高电平达到电源电平VDD以及大的驱动能力。фAO由фAS驱动,фAS通过T6向电容C及驱动输出管T10,T11充电。同时由打开的T4使T6关闭,以锁存在C等上的高电平。由于T4的漏端为低电平,所以T12、T13被关闭。这样,末级输出фAO上升到高电平。由于电容C的自举作用,使T10,T11的栅极电平上升到(VDD+VT)以上,фAO的高电平上升到电源电平VDD。

当恢复时钟фAOR达到高电平时,фAS、фAO都会恢复到低电平,而фAR恢复至高电平。фAO相对фAS应要求有一定的延迟时间,设计时这个延迟时间主要由фAS向C、T10,T11的充电时间所决定,也就是由T6与这些负载电容组成的RC延迟所决定。

虽然在DRAM中可能有几十种时钟发生器,但是它们的电路形式与上述的фAO时钟发生器基本类似。这些时钟在器件电路中主要完成三方面的功能:

1、对结点进行预充,使NMOS电路进行动态工作。避免直流功耗。如图3.28中的фAR、图3.27中的фL都是属于完成这种功能的时钟。

2、通过自举作用,使达到高的输出高电平。如图3.28中的фAO等就是这类时钟。

3、满足电路工作的时序要求。如图3.28中的 地址锁存时钟,它必须在

地址锁存时钟,它必须在 和

和 下降后控制打开的地址缓冲器的门管,在完成地址输入后把它们锁存起来。利用DRAM中的这些时钟使整个电路从地址输入到数据读出能按要求的步序进行工作,不致出现混乱。

下降后控制打开的地址缓冲器的门管,在完成地址输入后把它们锁存起来。利用DRAM中的这些时钟使整个电路从地址输入到数据读出能按要求的步序进行工作,不致出现混乱。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助