电子技术论坛

信息来源: 时间:2022-3-28

详解灵敏恢复(S/R)放大器的工作原理和分析

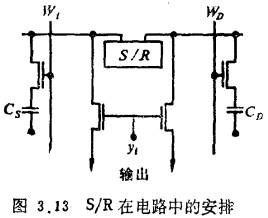

S/R放大器实际上是一种特殊的电压比较器。如图3.13所示,被比较的输入电压中一个是从选中单元读出,另一个是从虚单元读出,它们既是输入,又是输出。初始电平差经S/R的放大,使 的电平差拉开,形成“0”和“1”电平,通过y译码器向外输出。

的电平差拉开,形成“0”和“1”电平,通过y译码器向外输出。

此放大器除了放大功能外,还有恢复、刷新能力,这是DRAM电路所要求的。由于在 上预充的电平较高,对存“0”单元是破坏性读出。在读“0”过程中,Vs从0上升到(VDD-VTH),存“0”被破坏,要求经S/R放大后相应的位线降至“0”电平,由此将已破坏的单元回写“0”,称为恢复。

上预充的电平较高,对存“0”单元是破坏性读出。在读“0”过程中,Vs从0上升到(VDD-VTH),存“0”被破坏,要求经S/R放大后相应的位线降至“0”电平,由此将已破坏的单元回写“0”,称为恢复。

由前述可知,在保存状态下“1”电平会慢慢衰退,只有有限的保存时间,需要定期刷新,使“1”电平保持在它的最低电平限度以上。S/R放大过程中位线高电平可达足够高,它可以向“1”单元补充电荷的损失,起到刷新作用。

由此可见,DRAM的S/R不但具有放大功能,而且要对“0”单元进行恢复,要对“1”单元进行刷新。其关键是读出放大后,要使两边位线具有良好的高电平和低电平。

1、工作原理

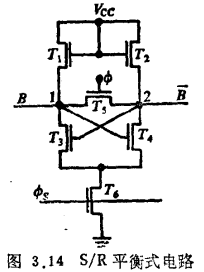

普遍采用如图3.14所示的平衡放大器形式。结点1、2分别连到位线 ,它们既是S/R的输入,又是输出。在读出之前,T 关闭,通过打开T5使节点1、2保持等电位平衡。读出时T5关闭,使读单元和对应的虚单元在

,它们既是S/R的输入,又是输出。在读出之前,T 关闭,通过打开T5使节点1、2保持等电位平衡。读出时T5关闭,使读单元和对应的虚单元在 两边建立一定的电平差,然后打开T6,由T1、T2、T3,和T4组成的触发器开始工作,使原来电平较低的一边降至“0”电平,相反一边升至“1”电平。这样就可以完成放大、恢复和刷新三种功能。

两边建立一定的电平差,然后打开T6,由T1、T2、T3,和T4组成的触发器开始工作,使原来电平较低的一边降至“0”电平,相反一边升至“1”电平。这样就可以完成放大、恢复和刷新三种功能。

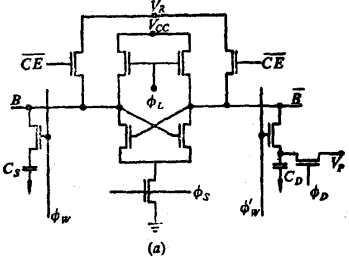

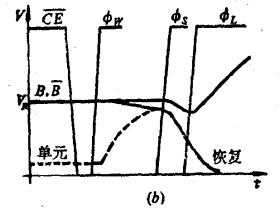

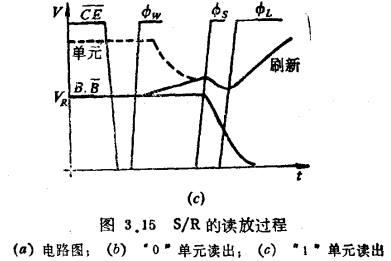

为了降低功耗,S/R应设计成动态形式。图3.15是一种早期的S/R半动态电路。首先由 时钟将

时钟将 应均衡地预充到VR电平,

应均衡地预充到VR电平, 关闭后打开单元和相应的虚单元的字线,其时钟为фw和ф'w,这时在

关闭后打开单元和相应的虚单元的字线,其时钟为фw和ф'w,这时在 上逐渐产生一个小的电平差。打开фs,

上逐渐产生一个小的电平差。打开фs, 的电平差得到放大。为了补充在读出过程中高电平的损失,由фL打开接电源Vcc的充电管,以得到较理想的高电平;但低电平一边的充电被放掉并消耗直流功耗。因此,这种S/R不是全动态,仅是半动态。图3.15(b)和(c)表示读出“0”单元和“1”单元的波形图。由图可见到“0”单元的恢复和“1”单元的刷新。该电路采用了半电压虚单元结构形式。

的电平差得到放大。为了补充在读出过程中高电平的损失,由фL打开接电源Vcc的充电管,以得到较理想的高电平;但低电平一边的充电被放掉并消耗直流功耗。因此,这种S/R不是全动态,仅是半动态。图3.15(b)和(c)表示读出“0”单元和“1”单元的波形图。由图可见到“0”单元的恢复和“1”单元的刷新。该电路采用了半电压虚单元结构形式。

这种S/R的主要缺点是功耗大。其原因为补充高电平时钟фL,打开时总有一个通路,要消耗直流功耗,由于在VLSI DRAM中S/R的数量很多(每条位线要有一个),所以总功耗是可观的。为此,应该取消фL时钟,设法使在读放过程中高电平的损失大大减少。

2、灵敏度分析

灵敏度是S/R最重要的指标,它是放大器能够正确检测两边电平差的最小值。“能正确检测”是指两边位线初始电平差的方向与读放后终态的高低电平相对应。

S/R的灵敏度越高,允许两边位线的初始电平差ΔV越小,那末CS/CB亦可以小一些。CS小可以节省面积,CB大可以加多一条位线上的单元数。因此,设计好高灵敏度的S/R对VLSI DRAM是十分重要的关键。

为了设计出高灵敏度的S/R,必须对影响灵敏度的主要因素进行较深入的理论分析。

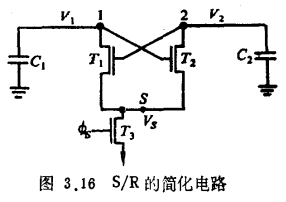

S/R的简化电路如图3.16所示,结点1、2分别连接两边的位线。设读出的初始电平差为ΔV=V10-V20>0,C1、C2分别为 的负载电容。为了分析方便,设фs打开T3,后Vs的电平以线性下降,即

的负载电容。为了分析方便,设фs打开T3,后Vs的电平以线性下降,即

其中K为下降速率系数。Vso为在T3关闭时通过T1、T2向S结点进行充电的平衡电位,应有:

其中VT2是T2管的开启电压。

由于V10>V20,初始时T2处于临界导通状态,T1处于截止状态。当T3打开后,V1、V2均会下降,但由于它们之间的反馈作用,最终会使一边为“0”电平,一边为稍低于起始电平的“1”电平。

当S/R两边完全理想对称时,即有

负载电容 C1=C2=C0 ;

开启电压 VT1=VT2=VT0 ;

跨导系数 β1=β2=β0 ;

那末,在不考虑外来干扰的条件下,理想的灵敏度是无限的,即只要有极小的ΔV,就能对它进行正确检测。实际情况并不如此理想,总会有一定的不对称性。经分析证明,不对称的程度是限制灵敏度的主要因素。

为了便于分析,我们先考虑理想对称的情况。当t≥0,打开T3,V1、V2随时间t的变化曲线如图3.17所示,可以把它分成三个区域:

(1)单管导电区(t0≤t<t1)

t0时刻Vs开始下降。于是V10-Vs>VT,T2导通,V2下降,而在这段短时间内,V30-Vs<VT,T1截止,V1维持V10不变。

由于T2工作在饱和区(V10-V20<VT),故有

其中的β0为(1.46)式中的β/2a。

由上式可见,V2的下降速率随t2而增加。

(2)双管导通区(t1≤t<t2)

由于Vs总是先比V2下降得快,因此在t≥t1时,(V2-Vs)≥VT,T1由截止变为导通,进入双管导通区。这时V1、V2同时下降,下降速度分别为

由于V1>V2,则有 。V1、V2在下降过程中的互相反馈,会使V1的下降速度变慢。

。V1、V2在下降过程中的互相反馈,会使V1的下降速度变慢。

当达到 ,即

,即 时,V1(t)到达了拐点,t=tM。此后V1的下降速度变慢,而V2的下降速度加快。

时,V1(t)到达了拐点,t=tM。此后V1的下降速度变慢,而V2的下降速度加快。

(3)恢复单管导电区(t≥t2)

当t=t2时,(V2-Vs)下降至VT,T1管截止,V1不再下降。当t>t2,V2继续下降,T2从饱和区进入线性区。V2最终随Vs降至“0”电平,而V1保持略低于V10的高电平。

通过以上对读放过程的详细分析,能够得到如下的结论:在理想对称条件下,S/R能对V1与V2之间微小的初始电平差进行正确检测。

但是,情况并不如此理想,总会存在一定的不对称性ΔC、Δβ和AVT。于是, 比较不只决定于V1和V2,而且与C、β和VT值有关,例如β1>β2,而ΔV。又比较小时,

比较不只决定于V1和V2,而且与C、β和VT值有关,例如β1>β2,而ΔV。又比较小时,

很可能比

很可能比 大,并先达到K,即V2先达到损点。最终V1降至“0”电平,V2保持高电平,与初始电平差恰巧相反,由此发生了误检。

大,并先达到K,即V2先达到损点。最终V1降至“0”电平,V2保持高电平,与初始电平差恰巧相反,由此发生了误检。

当C、VT、β存在一定程度的不对称时,为了不发生误检,必须要求初始的ΔV0=V10-V20足够大,以使 总比

总比 大,确保正确检测。在确定的ΔC、Δβ和ΔVT的条件下,总有一个使S/R不发生误检的最小ΔV0,这就是该S/R的灵敏度。当然,ΔV0越小,灵敏度越高。

大,确保正确检测。在确定的ΔC、Δβ和ΔVT的条件下,总有一个使S/R不发生误检的最小ΔV0,这就是该S/R的灵敏度。当然,ΔV0越小,灵敏度越高。

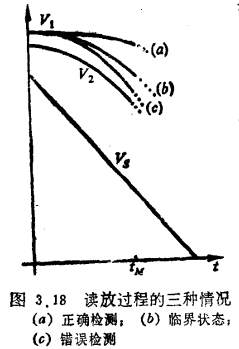

灵敏度显然与不对称程度密切相关。图3.18示出读放过程中的三种情形:正确检测、误检及两者之间的临界状态。临界状态的ΔV0就是我们要计算的灵敏度。由图可见,它在双管导通区应有 ,即V1、V2,下降线相互平行。由此可以进行如下推导:

,即V1、V2,下降线相互平行。由此可以进行如下推导:

由上两式:

利用 在=tM点相等,并等于K,则有:

在=tM点相等,并等于K,则有:

其中C0、β0是C和β的平均值。

由于V1、V2下降曲线在临界状态下是平行的,如果初始的单管导通区内V2下降比较小,则正确检测的条件为:

上式就是DRAM的S/R的灵敏度计算公式。由该式可见,对称性是决定灵敏度的关键。在不对称程度相同时,降低K、C0,增加β0,对改善S/R的灵敏度也是十分有利的。但是它们都有一定的限制。加大β0会使芯片面积增大;减小C0不利于增加一条位线上的单元数;降低及会使读放速度变慢。同时,这种无负载的全动态S/R虽有省功耗的优点,但是会使高电平有所损失。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助