电子技术论坛

信息来源: 时间:2022-3-10

MOS器件VLSI中内连线对延迟时间的影响的分析

随着单个器件尺寸日益缩小,性能改善,总的集成规模越来越大,VLSI的内连线对电路的时间延迟起着决定性的作用,已成为限制VLSI高速化的主要因素。

内连线的影响通过延迟RC反映出来。其中R、C分别为连线的杂散分布电阻和电容。连线电阻与线的尺寸及所用的材料有关,而与所用材料的关系更为密切。在VLSI工艺中可以采用多种材料作为连线,其电阻率越低越好。铝线的电阻率最低,为2.25×10-6·cm。但是,在VLSI的连线中不可能全部采用铝线,因为由此会给布线带来极大的困难。为了实现多层布线,还用掺杂多晶硅、扩散区、金属硅化物等。它们的电阻率都比铝高得多,特别是掺杂多晶硅的电阻率比铝要高2~3个数量级之多。

由于SiO2在硅集成电路工艺中作为介质有独特的优点,因此实用中仅需要考虑以SiO2为介质的布线电容。电容的大小不仅与布线面积有关,而且与场氧化层的厚度有关。厚度越大,布线电容越小,但在工艺上会产生困难。隔离场氧化层太厚,会使表面平坦度不好,容易产生在台阶处断铝等现象。

下面将分析VLSI中分布参量的延迟问题。

1、线延迟时间TL的计算

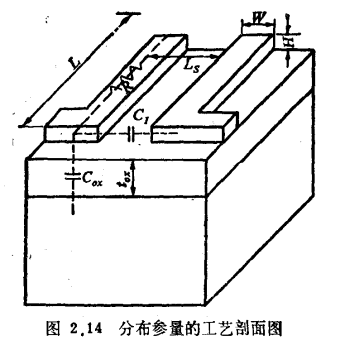

图2.14为分布参量的工艺剖面图。布线电阻由欧姆定律决定:

其中H为布线层的厚度。布线对衬底的电容

其中tox为场氧化层的厚度。

相邻布线之间的距离为LS,它们之间有钝化层(SiO2)隔离,其电容

总布线电容为两者之和,即

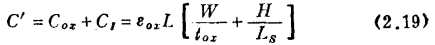

上述的平行板电容公式中没有考虑电场的边缘效应,故比实际电容偏小。实用的电容表达式为:

其中K1是一个大于1的因子。

根据分布延迟线(如图2.15)的瞬态输出响应公式(峰值设为1):

如果以从10%终值上升至90%终值为标准,延迟时间按(2.21)式计算得:

由上式可见,τL与布线各种尺寸及材料密切相关。

2、器件和内连线 Scaling-down的效果

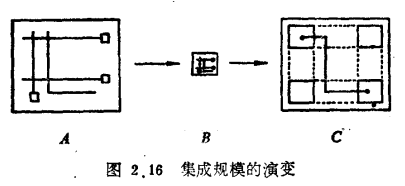

单器件尺寸缩小K倍,则延肘td缩短K倍,同时集成度亦应随之提高,由此信号传输的连线增多并加长。图2.16为说明上述情况的典型实例。A表示一个起始的单元电路,B为A按比例的缩小,C把多个B集成在一起。

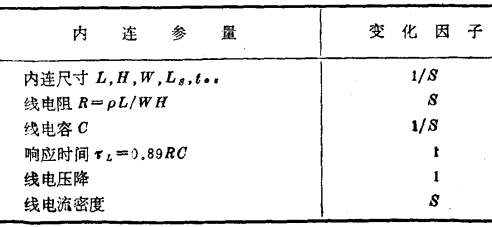

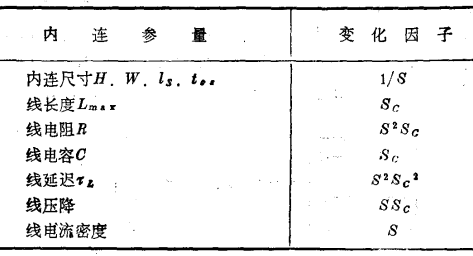

下表为从A到B局部连线按比例缩小后性能的变化,缩小因子为S。

由表可见,从A到B尺寸缩小S倍,线延迟保持不变,并不象器件本身那样延迟缩小S倍。这样,线延迟的矛盾更为突出。

当集成度和芯片面积加大时情况更为严重,布线延迟成为VLSI最终速度的限制。下表列出在C情形线长增加Sc倍时布线性能的变化结果。

由上表可见,线延迟τL增加了 倍,十分可观。芯片面积A越大,Sc越大。按统计计算结果:

倍,十分可观。芯片面积A越大,Sc越大。按统计计算结果:

3、VLSI平均线延迟的估算

设VLSI的最小光刻尺寸为λ,Ls=W=λ,合理地设tox=0.35λ,H=0.25λ,K1≈2,由(2.22)及(2.23)式:

由上式可见,A/λ2随工艺的进步而越来越大,所以降低τL的唯一出路是降低连线材料的电阻率ρ。

传统上,MOS电路中常利用掺杂多晶硅作为栅极和连线,但在VLSI中它的高电阻率成了致命的缺点。设法代替它的是耐高温的金属硅化物,如WSi₂、MoSi₂、TiSi₂、TaSi₂和CoSi₂等。

它们的电阻率为10~20μΩ·cm左右,比掺杂多晶硅下降一个数量级以上。

当然,采用多层铝也是一种良好的布线工艺方法,但它带来工艺步序的增加和困难,影响器件的成品率。随着工艺水平的提高,采用双层铝布线工艺已成为VLSI中较普遍的措施。

尽管采用了这些措施后情况有所好转,但布线延迟仍然是VLSI高速化的重要障碍。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助