电子技术论坛

信息来源: 时间:2022-3-4

详解MOS管器件的穿通特性及其工艺结构

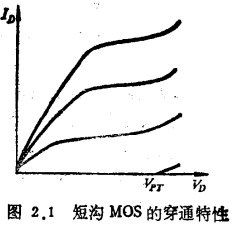

尺寸缩小,沟道缩短,首先碰到的问题是S/D穿通。实验发现,当VG<VT时,VDS达到一定值(即穿通电压VPT)后,IDS急剧增加,这种现象就是穿通。图2.1为MOS器件的穿通特性。

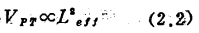

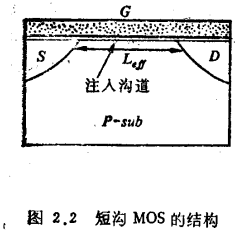

有效沟道长度越短,穿通电压VPT越低。经验的结果为:

因此,当Leff足够小时,如设计不当,VPT会小于VDD。这样,短沟器件无法正常工作。

为了保证在较短的Leff条件下能保持足够VPT,必须研究引起MOS器件穿通机理及应采用的工艺结构的改进措施。

一、机理

图2.2为短沟MOS器件的结构剖面。

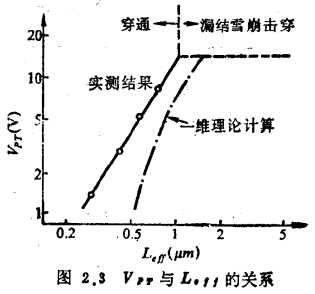

初期对MOS的穿通象双极型管一样处理,把S/D的耗尽区碰在一起的漏电压作为它的VPT或VDmax。实验发现,这样预估的VPT比实测值小得多。图2.3为VDmax与 的关系,图中的两条曲线是简单的一维穿通理论计算结果与实验的比较。

的关系,图中的两条曲线是简单的一维穿通理论计算结果与实验的比较。

如果将双极型穿通公式套用于MOS器件,可得:

图2.3上的理论计算曲线就是按上式而得。

MOS穿通电压的机理与双极型有如下两点不同之处:

1、双极管的发射结处于正向,载流子向基区注入。MOS管的源极不是正向,而是反向或零偏。因此,即使S/D的耗尽区碰在一起,S区的电子流会受到势垒的阻挡而不致发生穿通。在VDS足够大,器件沟道比较短的情况下,S区势垒大大降低,发射流加大并为D区所收集,这时才有明显的穿通电流。这也是前述的较严重的DIBL现象。

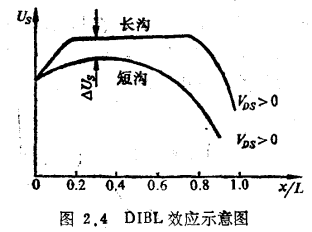

图2.4为DIBL效应的示意图。横坐标为归一化的沟长,纵坐标为S/D之间电子势垒的分布,ΔUs表示源势垒下降。由图可见,随着L缩短,VDS加大,S区势垒随之下降。

与穿通相关联的是次开启漏电。第一章第八节中已分析过,当VG<VT,VDS加到一定大时,因DIBL效应出现次开启漏电。如果VDS足够大,次开启漏电也足够大,就认为发生了穿通,实际上两者没有严格界线,只是DIBL效应的严重程度不同而已。

2、表面栅电位的存在会对穿通起抑制作用。正如第一章第六节所分析,漏栅之间存在着电场,使漏电场的部分电力线结束在栅极上,漏耗尽区减小,漏电场受到屏蔽,因而S区势垒下降减少,不容易发生穿通。

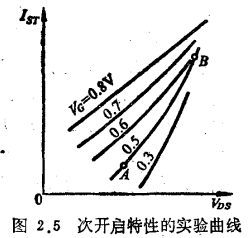

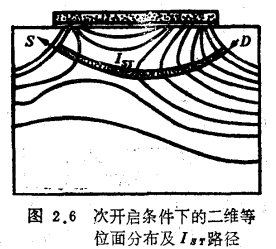

图2.5为VG<VT时,在不同VG的情况下,次开启漏电流IST与VDS的实验关系曲线。由图可见,当VDS不太大时各曲线是分散的,VG越高,IST越大。但当VDS足够大时,各曲线汇聚到一起,到达B点附近。一般把B点称为穿通点。这种聚合现象与器件的二维电场分布有关。图2.6为在VG<VT条件下,当VDS=5V时求解二维泊松方程所得的S/D之间的等位面分布。由图可见,等位面呈马鞍形分布,电力线垂直于等位面,IST在次表面流动,受VG影响较小。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助