电子技术论坛

信息来源: 时间:2022-3-4

MOS器件尺寸缩小及其限制和典型工艺参量表

Scaling-down的基本原理

Scaling-down或称等比例缩小,首先在1974年由Dennard提出。其指导思想是在MOS器件内部电场不变的条件下,通过纵、横向尺寸的缩小,以增加跨导和减少级联负载电容,由此可以大大提高电路的性能。同时要求电源电压与尺寸按同样比例下降。这样,使器件与电场有关的非线性因素(如迁移率)也不会因此而改变。

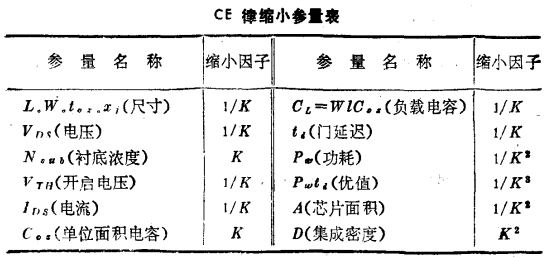

这种缩小规律称为CE律,即恒场律。下表列出CE律的缩小规律及所得到的结果。

上表中的K是缩小因子。从表可见,器件性能从Scalingdown得到很大的好处,主要体现在电路优值 ,即功耗延迟积,减小

,即功耗延迟积,减小 倍。这是由于Scaling-down,VDS缩小了K倍,IDS和td也缩小了K倍,这三个因素都对减小器件的功耗延迟积有利。

倍。这是由于Scaling-down,VDS缩小了K倍,IDS和td也缩小了K倍,这三个因素都对减小器件的功耗延迟积有利。

对IDS和td的缩小作简单证明如下:

由第一章(1.43)式:

其中VDS,(VGS-VTB),W,L均应缩小K倍,Cox增大K倍,结果IDS还是缩小K倍。

延迟时间 ,其中VDS、CL(负载电容)、IDS均1os缩小K倍,故td也缩小K倍。

,其中VDS、CL(负载电容)、IDS均1os缩小K倍,故td也缩小K倍。

W、L的缩小使集成同样数目管子的芯片面积缩小K2倍,即集成密度提高K2倍。

由上可见,Scaling-down的实现成为VLSI技术的基点。十几年来工艺技术和器件物理的研究和开发都是围绕这个基点进行的。正是由于这方面的不断进步和成功,使当前集成电路发展到如此高的水平,器件尺寸已缩小到亚微米级,集成度已经超过了百万器件/片。

简单的CE律缩小还存在一些问题:

1、VTB缩得太小会减弱抗干扰能力,引起关闭时次开启漏电的增加,不利于动态结点电平的保持。由第一章(1.132)式可知, ,而VTB越低,关闭时的

,而VTB越低,关闭时的 越大,故

越大,故 增加。

增加。

2、源漏耗尽区宽度并不按比例缩小K倍。应有

式中l为S或D, 为pn结内建电势。当

为pn结内建电势。当 不成立时,耗尽区宽度缩小不到K倍,由此,随尺寸缩小横向电场增强,破坏CE规律。

不成立时,耗尽区宽度缩小不到K倍,由此,随尺寸缩小横向电场增强,破坏CE规律。

3、电源电压标准的改变带来不便。因为目前用户习惯使用5V标准电源,改变电源电压会需要改变整机中一切有关的元器件。同时电源电压的下降会使噪音容限下降,而要重新考虑抗噪音措施。

最近提出的片内限压器是解决该问题的一种良好途径。外面仍采用5V电源,但通过一个片内限压器到片内小尺寸电路。限压器的输出电压一般为3V左右。

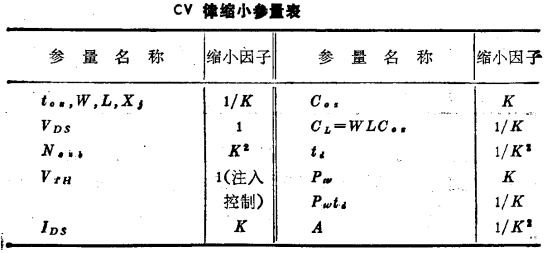

由于CE律存在上述问题,因此有人提出采用CV(恒压)律,即保持VDS及VTB不变。但是CV律对器件性能的改进远不如CE律。其结果列于下表。

从上表可见,CV律对电路性能的提高远不及CE律,优值因子只有1/K。采用CV律必然使沟道内电场大大增强,由此带来一系列问题,特别是热电子效应和载流子速度饱和。这些效应对改善电路性能和稳定性是极为不利的。此外,由于功耗增加了K倍,面积减小了K2倍,造成功率密度增加K3倍,由此又造成器件散热困难及铝线电迁移等问题。

总之,CV律并不适用沟道很短的器件,一般只能用 的VLSI。

的VLSI。

由上表可见,为了减小S/D耗尽区的宽度,把 提高K2倍也不合适。这样会使pn结的寄生电容大大增加,降低器件的速度。提高

提高K2倍也不合适。这样会使pn结的寄生电容大大增加,降低器件的速度。提高 的目的是防止S/D的穿通,而这种穿通仅发生在栅下区。因此,完全没有必要改变

的目的是防止S/D的穿通,而这种穿通仅发生在栅下区。因此,完全没有必要改变 ,只要通过合适的栅区防穿通离子注入就可以达到目的。这一点我们将在下一节作较深入的分析。

,只要通过合适的栅区防穿通离子注入就可以达到目的。这一点我们将在下一节作较深入的分析。

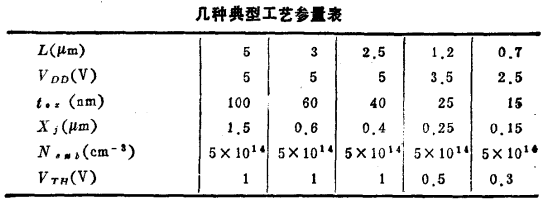

根据上述情况,实际应用的缩小律既不是CV也不是CE,而是按实用和工艺的可能进行折衷。下面我们根据有关资料列出几种工艺选定的典型参量。

上表中的 保持不变,以保证小的pn结寄生电容,以免影响电路速度。

保持不变,以保证小的pn结寄生电容,以免影响电路速度。 时保持5V电源。

时保持5V电源。 时电源适当降低。但由于受噪音容限的限制,一般VDD要保持在2.5V以上。

时电源适当降低。但由于受噪音容限的限制,一般VDD要保持在2.5V以上。

Scaling-down技术实际上涉及两方面的关键技术问题:

1、工艺技术为实现缩小尺寸而要解决有关的工艺设备和工艺方法。主要包括精密制版、光刻、浅结、高质量超薄氧化层、精确离子注入控制等。

2、器件物理 分析小尺寸器件的各种副效应,并研究如何进行抑制的措施。

本文不涉及工艺技术问题,仅讨论器件物理方面的问题。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助