电子技术论坛

信息来源: 时间:2022-2-25

MOS场效应管源漏寄生串联电阻的影响

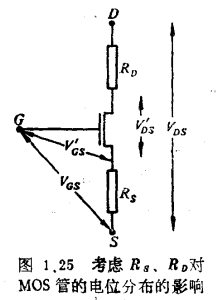

随着器件尺寸的缩小,S/D区pn结深度变浅,接触孔面积变小,使源漏区的寄生串联电阻Rs、RD变大。图1.25表示存在Rs、RD情况下器件的电位情况。

Rs、RD作为器件的一个寄生元件是采用任何一种测量手段都不可避开的,也是在电路模拟中必须考虑的重要因素。

由图可得:

先考虑VDS比较小的情况,在线性区有

其中θo是不考虑Rs、RD的迁移率修正系数。

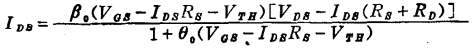

将(1.61)及(1.62)代入(1.63)可得:

化简:

由于IDS、VDS较小,所以忽略它们的二次方项,可得如下的简化公式:

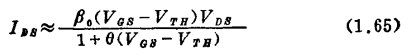

其中

由此可见,可以把源漏寄生串联电阻的影响等效成有效迁移率纵向场衰退系数θ的增加。

RS、RD使IDS下降,器件跨导gm下降。因此,它是提高短沟器件速度的不利因素,应该在工艺上采取措施减小它们。

值得注意,公式(1.65)与(1.66)是在VDS、IDS比较小的条件下推出的,但公式(1.66)已作为一个通用公式在各种VDS下应用。当VDS较大时不可避免会带来较大的误差。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助