电子技术论坛

信息来源: 时间:2022-1-26

MOS晶体管共栅-漏电路及其N-P沟道电阻性组态详解

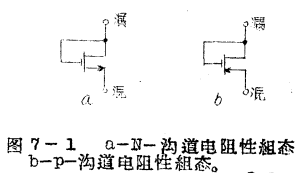

在MOS集成数字阵列中很少使用扩散电阻,而双极晶体管阵列通常都有扩散电阻。为了避免制造扩散电阻而增加工艺步骤,共栅-漏的MOS晶体管可以作为逻辑电路的电阻性负荷。P-沟道和N-沟道元件作为电阻性负荷的组态示于图7-1。

先来考虑N-沟道的组态。对于N-沟道增强型器件而言,夹断电压(或者称阈值电压)总是正的,用VP来标记它。当VD>VG-VP时,MOS晶体管的工作就超越夹断而进入饱和区。对于图7-1a所示的电路组态,相对于源而言;VD=VG。

因而饱和条件总是满足的(因为VP为正的),也就是VD=VG>VG-VP (7.1)

换一句能来说,漏-源电压低于雪崩状态时,共栅-漏组态总是工作在饱和区。不过,只有在漏-源电压超过阈值电压VP时电流才开始流动。在第三章,已经看到,漏电流与栅压服从平方律的关系。

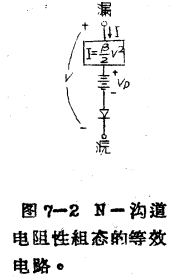

在论及的共-漏组态中,漏电压等于栅压,因而

漏-源电压为低负压时,晶体管截止,因而没有电流流动,对于正栅压在-源电压未超过VP之前也是没有电流流动的(方程3.36)和(7.2)只有在VD>VP时才成立〕VD>VP时电流就依平方律而增大。共栅-漏组态的等效电路由平方律器件,电池与理想二极管串联起来便可构成。等效电路示于图7.2。

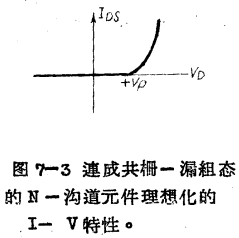

共栅-漏负荷电路实际上不是电阻性的,更加恰切地说,当电路置于适当的偏压时,此电路是一个与“补偿”电池串接起来的平方律电路。不过,数字从开态转变为关态时,所谓“电阻性”负荷的平方律特性并不破坏电路的工作。可以期望,N-沟道组态的I-V曲线应与图7-3相仿。

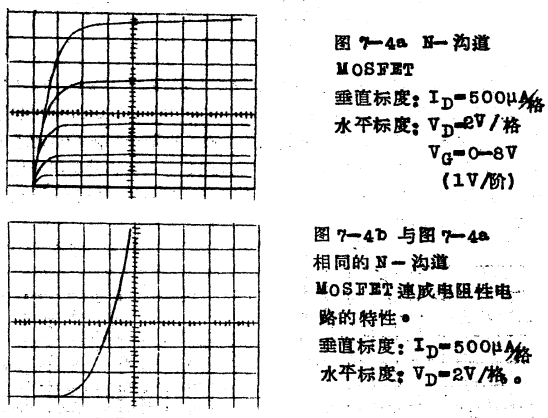

阈值电压为3伏的N-沟道增强型器件,其实际的I-V曲钱示于图7-4,此曲线与图7-3的曲线十分吻合。

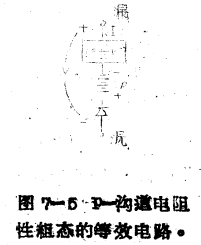

应用相似的分析,P-沟道组态的等效电路可以画成图7-5那样。

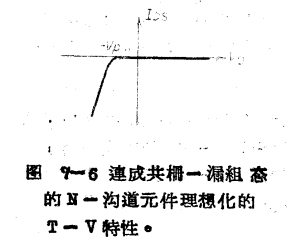

P-沟道电阻性组态,其预期的特性示于图7-6。

又一次看到,P-沟道器件预期的特性与真正的I-V特性曲线(如图7-7a所示)之间得到十分良好的吻合。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助