电子技术论坛

信息来源: 时间:2022-1-13

解析MOS管饱和之外雪崩击穿区的导电情况

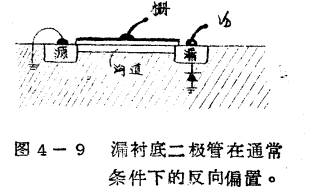

在通常的工作条件下,MOS晶体管中的漏二极管为反向偏量。对于N-沟道的元件,这种情示于图4-9。假定恒定的电压加到栅极上,随着漏电压的增大,MOSFET就跨进恒电流的饱和区。不过,漏电压要是继续增大,器件的特性越过饱和区而进入漏电流再度增加的区域。起初增大较为缓慢,随后就变快起来。

上述效应是反向偏置漏二极管开始击穿的结果。然而,正象就要看到的那样,实际的击穿早在二极管预定的体内击穿发生之前就开始了。 可以相信,硅表面接近于二极管结的栅极对于雪崩提早发生应负主要“责任”。当然,用以制造漏和源区的浅扩散对此也有一定的作用。

现在来研究一下雪崩击穿的机构。对于所有实际的情况,电场仅仅加在反向偏置P-N二极管结的耗尽区。耗尽区中电场强度随反向偏压的增加而增大。当反向偏压足够大而使耗尽区中的场强达·到105伏/厘米左右时,雪崩击穿就发生了。雪崩击穿是由于通过耗尽区的任何载流子受到强场的飞快加速而引起的。平均地说,载流子受到加速时,它们将渡过一段路程“λ”。然后,每个载流子都和晶格中的硅原子发生碰撞而被散射。(λ为均自由路程)。如果电场足够高,加速度就可以大到如此的地步,以致于电子与晶格原子发生碰撞时,其速度和动能足以将硅原子外轨道的电子打出来。这样就有两个自由电子,每个电子又被电场加速;第二次碰撞又有更多的电子被打出。上述过程相继发生变键锁反应。由此产生了许多导带电子而使反向电流迅猛增大。只有在电场强度足够高而使电子在快要碰撞时就被加到某一个速度Vo雪崩击穿才能发生。

即

Vf为第一个电子在碰撞之后的最终速度,而EI为硅原子中外轨道电子的电离能。反向偏压越大,电场强度越高,雪崩击穿就更快地发生,反向电流也就更大。当反向偏压达到击穿电压VB时,大规模的击穿就发生了。

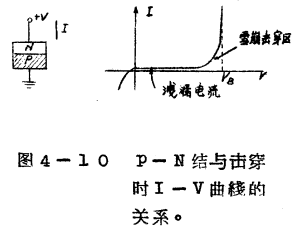

对于所示的P-N结,其I-V特性如图4-10所示。

大家知道,在反向偏置的P-N结,绝大部分的耗尽区都位于电阻率较高的一边。因而反向偏置P-N结(此P-N结的一边电阻率较另一边高得多)的体内击穿电压实际上仅是高电阻率区掺杂浓度的函数。得马上就会看到,几何结构对于决定雪崩击穿电压也是一个重要的因素。MOS管雪崩击穿。

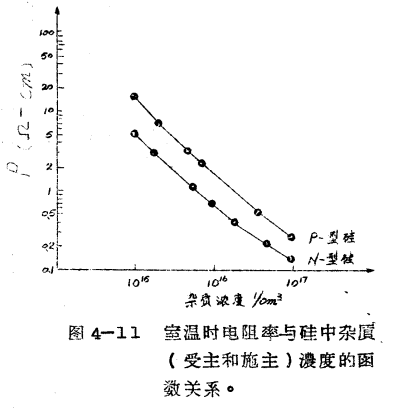

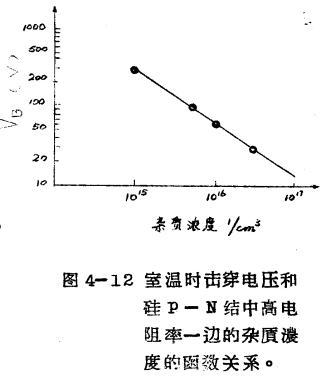

如果假定P-N结两个区的界面即长又宽,而P区的电阻率比N区的电阻率高得多(N-沟道器件就是这样),那么,雪崩击穿电压就可以通过图4-11和图4-12的图解来决定,这两个图实验上已经测定过。

只要知道P区的电阻率,由图4-11就找到每立方厘米受主的掺杂浓度。然后再用图4-12就可决定雪崩击穿电压的数值。MOS管雪崩击穿。例如,1Ω-cmP-型材料相应的受主掺杂度,每立方厘米构为1.8×1016;而结的击穿电压则为40伏。要记住,得到这个击穿电压要求两个区的界面既平坦又宽广。这就是所谓的“体内雪崩击穿”,其数值总比漏二极管的击穿电压高,因为后者的击穿电压还受到几何结构以及表面状态等因素的影响。

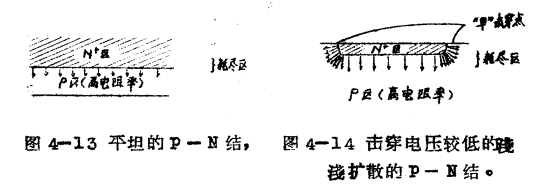

在许多浅结的情况,几何因素将导致雪崩击穿电压的降低。通过下面的讨论,对此便可一目了然。雪崩击穿电压是P-N结耗尽区中电场的函数。如果耗尽区中电场的分布不均匀,场强最高的地方就首先击穿,可以理解,某些结的几何结构会改变电场的分布并且使电场集中到某个区域,从而使这些地方易于击穿。这种效应示于图4-14中,图4-13表示一个电场分布均匀的不坦的P-N结,其击穿电压由图4-11和4-12就能计算出来。图4-14跳明了扩散结中曲率最大的地方,场强最高。这些地方首先经受着反向击穿。因此,图4-14结构的击穿电压定比图4-13低。总而言之,对于结构(图4-14及其相仿结构)引起击穿电压显著变化的情况,其场强很高的耗尽区宽度定与扩散深度可以比拟甚至更大。

一般地说,如果P-N结界面有明显的弯曲(曲率半径较耗尽区宽度小),与相仿的平担结相较,其界面任何地方的击穿电压都要低一些。用存在强电场的导体能够做一个很生动的模拟实验。击穿(例如,导体间隙发出火花)系发生在导体上的某些点上,而这些区域正是曲率最大的地方。同样地,P-N结的击穿也是发生在曲率最大的地方。

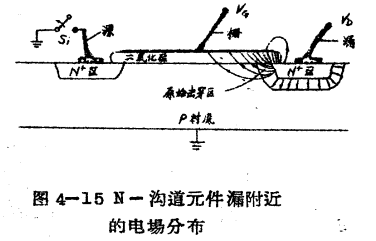

现在再来扩大我们的讨论范围。几何结构并不是影响P-N结电场分布的唯一因素。譬如讲,一块半导体接近于P-N结也会引起耗尽区中电场的再分布。事实上,MOSFET就是有这种情况。实验上也观察到,如果MOS器件的栅极不复盖,其漏-源击穿电压比复上栅极后的击穿电压要高得多。MOS管雪崩击穿。 如图4-15所示,栅极引起电场的再分布从而产生高电场就解释了这种现象。这个区是造成漏-源击穿电压降低的主要因素。氧化层较薄时,改变衬底电阻率对于击穿电压的影响甚微。

倘若靠近二极管P-N结的地方存在着金属电极对于雪崩击穿电压有这么大的影响,可以想象,电极上施加电压对于击穿电压也应当有所影响。如果MOSFET的源极不接,让它开路,那么,漏对其导电过程就不起作用。再参看图4-15,开关打开时,源就与电路隔开。对于这种N-沟道元件,相对于衬底,栅极加上负电压会使原来击穿区的场强进一步增大,这更有利于击穿过程的发生,从而造成漏极击穿电压VB的降低。相对于衬底而在栅极上施加正电压,情况就恰恰相反。也就是原来击穿区的场强减弱,而击穿电压增高。当然,击穿电压再增高也不会超过图4-11和4-12所计算出来的体内击穿电压值,因为体内击穿不受半导体表面的影响。

和N-沟道元件相似,对于P-沟道元件正的栅-衬底电压降低了VB值,而负的栅-衬底电压则增高其VB值,如果源接地,而晶体管仍工作于正常的状态,用电流流经沟道,电力线又重新分布,其影响就变得加复杂。

虽然很少把MOSFET偏置在雪崩的状态,但是利用雪崩击象随栅压而变化的原理,Nathanson,Atalla,Shookley等人已研制成功其他结构类型的MOS器件。利用这种MOS器件能够进行雪崩击穿的放大和电场调制。

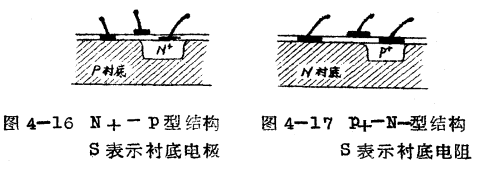

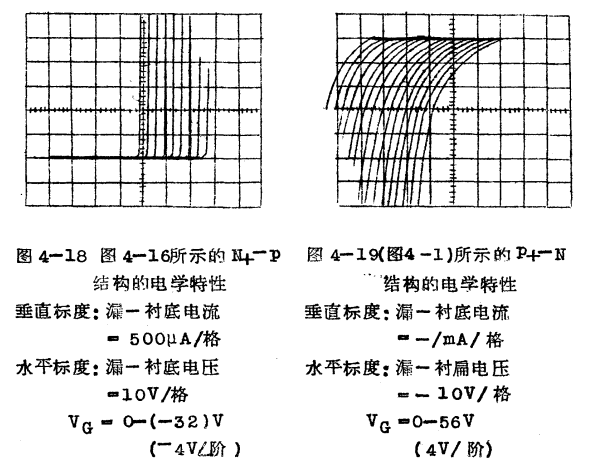

现在来考虑一下图4-16和4-17所示的结构,显而易见,当MOS晶体管的源断路时,两者的雪崩击穿与栅压关系是完全相同的。

尺寸与典型的MOSFET相当的这两种结构,其实的I-V特性曲线(可见其雪崩击穿是栅压函数)示于图4-18和4-19。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助