电子技术论坛

信息来源: 时间:2022-1-11

MOS管器件夹断之前可调电阻区的导电情况解析

正象我们看到的那样,在MOS晶体管中,漏和源之间的电导是栅极电压的函数。实质上,这是沟道电阻随栅压而变化的结果。对于漏源电压比较小而低于夹断的情,漏和源之间的电流通道仅仅由导电材料所构成·然而,漏源电压较高时,在漏区附近便开始形成耗尽区,从而把沟道夹断。漏源电压进一步增大,电流就发生饱和,而器件就工作于区2。

如果我们来考虑漏-源电压较低,好象VD<<VG-VP的情况,可以预料,此时器件应工作在可调电阻区。VP为夹断电压,定义为第三章所述。(当发生夹断时,沟道中接近于漏区的地方,其可移动的电荷密度趋于零,因而形成了耗尽区·)

沟道未被耗尽区阻塞时,MOS器件漏-源的 关系呈现出可调电阻的特性,因而能够期望。

关系呈现出可调电阻的特性,因而能够期望。

式中C为常数,其数值是栅极电压的函数。Ihantola发现漏-源电压低于夹断时。

β为第三章所定义,整理而得:

上式可表示为

式中C(VG)等于β(VG-VP)而△(VD)等于 。在可调电阻区,漏-源电压受VD<<VG-VP限定因而,

。在可调电阻区,漏-源电压受VD<<VG-VP限定因而,

这样,我们便可断定,△是一个很小的修正因子,在漏源电压较低时,此因子可略而不计。随着漏-源电压的增大,修正因子△的影响也随之变大,而使I-V特性曲线的斜率变小,从而破坏其电阻的线性关系。总之,只有在漏-源电压较低时才能获得线性良好的可调电阻区。

当漏-源电压近于夹断但仍然在区1的范围时,(4.2)必须加进另一项,这一项将进而使曲线变平。在稍为低于夹断的情下:

式中

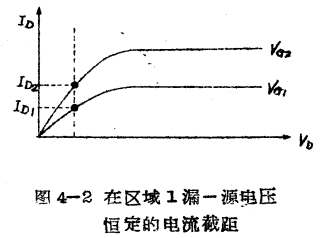

在区1中,栅压数值较高时,(4.6)和(4.2)式需要进一步修正。其原因如下所述。考虑一下图4-2的N-沟道MOS晶体管的特性。VD为区1内的漏源电压,令ID1,ID2,VG1和VG2的定义如图4-2所示,所有的情况漏电压VD均为恒定,对于夹断之前的VD,

而

(4.9)减去(4.8),得到

如果把修正项 加到(4.8)和(4.9)式,(这与漏-源电压接近于夹断的情况相应)其结果应与获得的(4.10)完全相同。

加到(4.8)和(4.9)式,(这与漏-源电压接近于夹断的情况相应)其结果应与获得的(4.10)完全相同。

VG1和VG2,(因而ID1和ID2)是人为地加以选取。因而,(4.10)就告诉我们,不管原来的VG数值如何,给定的VG变化将引起相应的ID变化。换一句话说,如果Cd是一个随漏-源电压而变化的常数,那未Ihantola方程式就指出,漏电流的变化就等于Cd乘上栅压的变化。因而,这个关系式表达为

栅压较高时,(4.11)就不成立。

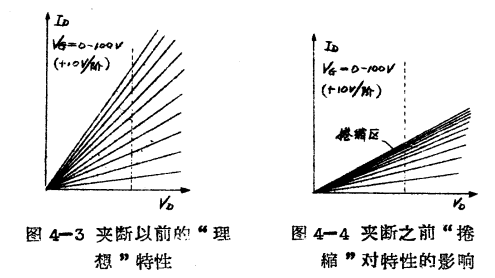

举例而言,在区1保持VD恒定的情况下,如果栅压从1伏增加到2伏,漏电流相应地增大100微安,那末,由方程(4.10)和(4.11)可知,栅压从25伏上升到26伏时,漏电流也应当增大100微安。如果栅压较高时,(4.10)和(4.11)也成立,那么漏电流随栅压增大而增大的速率应保持不变。这样一来,栅压很高(但仍然低于栅极绝缘层的击穿电压)时,工作于夹断之前的器件,其源漏电阻可能趋于零,显然,这是不符实际情况的,因为漏和源的金属接触电阻,键合引线的接触电阻以及源,漏本身的寄生电阻都将导致漏源之间存在一定的串联电阻。另外,当绝缘层上存在着与电流方向垂直的强电塌时,沟道中载流子迁移率将会减小。正象![]() 2.2节所述的那样,这种效应是由于绝缘层上的强电场把载流子吸引到界面,从而引起其他散射过程而导致的结果·栅压很高时,迁移率的减小反映出β的相应减小。因为β与以是成正比的。β的减少自然会引起栅压很高时的曲线叠合起来)这样,便可预料,栅压很高时,曲线的阻值(即斜率的倒数)趋于一个极限值,此与图4-4所示的“捲缩区”相应,当然,曲线开始激烈的捲缩所需的栅压随晶体管的不同而有所变化。

2.2节所述的那样,这种效应是由于绝缘层上的强电场把载流子吸引到界面,从而引起其他散射过程而导致的结果·栅压很高时,迁移率的减小反映出β的相应减小。因为β与以是成正比的。β的减少自然会引起栅压很高时的曲线叠合起来)这样,便可预料,栅压很高时,曲线的阻值(即斜率的倒数)趋于一个极限值,此与图4-4所示的“捲缩区”相应,当然,曲线开始激烈的捲缩所需的栅压随晶体管的不同而有所变化。

上面论及的两种主要机构(即串联寄生电阻和电场引起沟道迁移的减小),究竟哪一种机构占优势仍在议论纷纷而无定论。栅极电场较高时造成曲线捲缩的原因有两种不同的看法,为电场引起迁移率减小是主要的,而H 和

和 却忽视迁移率的因素,相反地认为寄生电阻是主要的。当然,元件不同,其每种机构影响的程度也有所差异,不过,只要了解用以解释“捲缩”的模型,因而迁移率变化的因素可以到有效的串联电阻中。这种模型可以在漏极或者源极上附加一个串联电阻,也可在两个电极上各自附加一个电阻。将根据这样的模型-把有效的串联电阻置于理想的MOS器件(所谓理想的MOS器件即漏-源电压低于夹断时,它从

却忽视迁移率的因素,相反地认为寄生电阻是主要的。当然,元件不同,其每种机构影响的程度也有所差异,不过,只要了解用以解释“捲缩”的模型,因而迁移率变化的因素可以到有效的串联电阻中。这种模型可以在漏极或者源极上附加一个串联电阻,也可在两个电极上各自附加一个电阻。将根据这样的模型-把有效的串联电阻置于理想的MOS器件(所谓理想的MOS器件即漏-源电压低于夹断时,它从 方程)的漏极回路上-来进行讨论。另外两种模型可仿效处置。

方程)的漏极回路上-来进行讨论。另外两种模型可仿效处置。

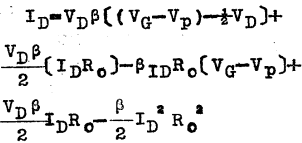

把一个“真实世界”MOS晶体管假设为如下的模型。这个模型为一只小电阻Ro与理想MOS晶体管(即栅压很高时漏-源电阻趋于零的晶体管)的漏极串联。具体模型示于图4-5之中,由于理想晶体管在低于夹断时应服从(4.2)。因而在A点就得到

在模型中,非理想晶体管真正的漏极是B点。漏电流ID也流经串联电阻Ro所以

如果以(4.13)代人(4.12)便有

或者

倘若修正项IDRO很小,以至于ID2RO2与其他各项相比可以略而不计,整理上式得到

因而

或者

这样

显而易见。(4.14)给出了正确的关系。栅压低到尚未发生捲缩的情况。

(4.14)便简化为(4.2)的形式。栅压高到足以发生捲缩时。

而

那么分母的第二项就变成优势项,漏电流就趋于串联电阻存在时的极限值。那就是

由上式可见,栅压很高时,与RO相比,理想的MOS器件实上是短路的,而其器件在夹断之前的I-V(漏-源特性实际上也就是有效串联电阻的特性。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助