电子技术论坛

信息来源: 时间:2021-12-28

解析制作微米沟道长度MOS场效应晶体管的扩散-自对准技术

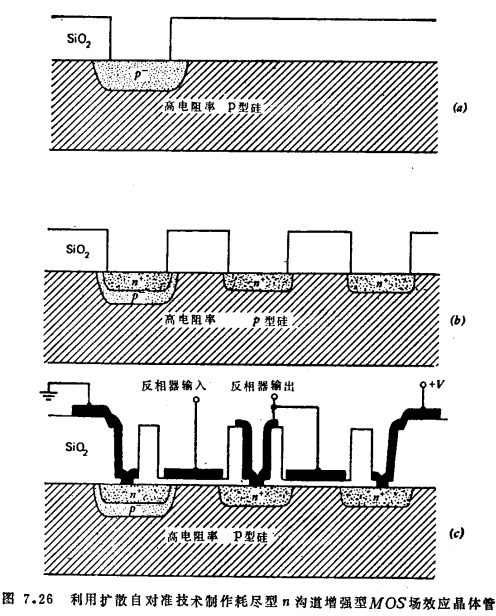

哈里斯(Harries)76首次提出并成功地证实应用扩散-自对准结构的概念制作有效沟道长度约为1-2微米的n沟道增强型MOS场效应晶体管。哈里斯(Harries)在高电阻率p型硅衬底上制作了这种器件,方法是首先局部腐蚀二氧化硅掩模层,为源扩散确定窗口,在完成低浓度p型(硼)扩散之后,随着进行延时驱进,以降低硅表面的有效掺杂浓度,和在除了源区窗口边缘以外的p区进行侧向扩展。接着在保留源区窗口情况下,对二氧化硅掩模层进行腐蚀,以确定漏区。这时,进行高浓度n+磷扩散以构成漏区和源区,接着用标准MOS制作技术以通常的方法完成器件的加工。因为低浓度p扩散向源区以外的地方作侧向扩展,并由于p型衬底有比较高的电阻率,两个n+区之间留下的硅表面即使栅极电压为零时也发生强反型,器件的有效沟道长度完全随p型扩散区相对于扩散n+源区边缘进一步作侧向扩展的程度如何而变。典型情况是器件沟道长度约为1.5微米。扩散-自对准技术与上节描述的离子注入方法不同,它不需要极严格的腐蚀工艺以确保微米级线宽,因为沟道长度本身完全由p和n+扩散的扩散剖面来决定,并且因为自源区窗口向外进行双扩散而使沟道自动对准源区;但是,对p扩散形成的最后的表面浓度,必须保持极精确的控制,这对于确定器件的阈电压特别重要。

如图7.26所示,同样的工艺技术很容易加以推广用来制作由增强型有源器件和耗尽型负载元件所构成的n沟道MOS集成电路77。这种电路的优点是众所周知的,已经由林(Lin)和瓦克(Varker)78进行过研究。塔路伊(Tarui)、哈亚希(Hayashi)和塞基格瓦(Sekigawa)77用这个方法制成了具有耗尽型负载元件的高速MOS或非门,其特点是当工作条件为+5伏电源和对应于三个扇出端的容性负载时,开关时间约为1毫微秒。有源MOS场效应晶体管的典型阈电压约为+2伏。由于各个有源MOS场效应晶体管具有亚微米级的沟道长度,并且因为器件是用高电阻率p型硅衬底制成的,所以观测到很高的跨导和低“导通”电阻,同时相对于衬底的结电容相当低。因为利用的是p型衬底,沟道区并非浮置,而对衬底有直接的欧姆接触。所用的制作技术,如图7.26所示,除通常的MOS集成电路技术之外,尚要求附加一道光刻工序和一道扩散工序。

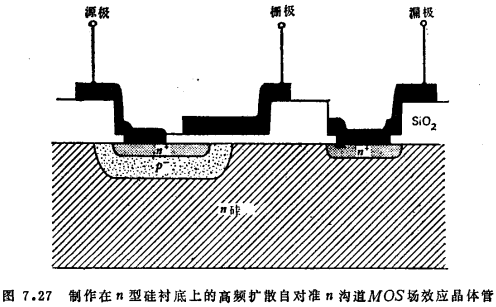

考奇(Cauge)和科克西斯(Kocsis)79提出的报告指出:采用扩散-自对准技术,在n-型硅衬底上,也制成了类似的器件。这种器件的截面图见图7.27,制作这种器件的技术与塔路伊(Tarui)、哈亚希(Hayashi)和谢基格瓦(Sekigawa)应用的技术非常相似,同时采用n型衬底使漏-沟结的耗尽区可以扩展到高电阻率n区,而不进入沟道区,从而消除了通常由于考虑到穿通而加在器件上的最高漏极电压的限制,而且产生的栅-漏反馈电容很小。器件是在载流子速度饱和状态下工作,而且发现器件在饱和漏电流区的电特性与方(Fang)和克劳德(Crowder)75观察到的结果很相似。不难看出如图7.27所示的MOS场效应晶体管结构应用到集成电路时,各个器件之间需要某种形式的隔离,假如不这样作,所有晶体管的漏区彼此将会直接接通。考奇(Cauge)和科克西斯(Kocsis)还描述了利用薄膜硅-绝缘物结构和p-衬底制作这些器件,而p-衬底上有把各个器件隔离起来的,用外延生长的n-硅薄膜。后一技术有利之处是如果使自源窗口向外进行的低浓度p扩散,通过n外延层扩展而进入到p型衬底,那么沟道区将能够同衬底做欧姆接触,结果沟道不再浮置。由在各个晶体管周围设置另外的p扩散区来为结提供可靠的隔离,这种方法与双极外延集成电路中普遍用来隔离共集电极区的技术完全类似。

考奇(Cauge)和科克西斯(Kocsis)提出的报告指出:在相当千兆赫以上的频率下,器件还有相当高的增益。对反相器结构测量了晶体管的开关速度。测得的结果是:上升时间为0.48毫微秒,延迟时间为0.27毫微秒。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助