电子技术论坛

信息来源: 时间:2021-12-23

分析应用离子注入技术改变MOS场效应器件的观测阈电压

虽然,制作MOS场效应晶体管和集成电路,最先应用离子注入技术的目的是用栅电极作为掩模,以减小寄生的栅-漏和栅-源电容,而且还注入与再现高表面电阻率的线性电阻。不久就显而易见利用离子注入技术来改变MOS场效应晶体管的阈电压也许是更为重要的应用。特别是,人们发现,只要穿过器件栅极绝缘物对其下的硅衬底注入浓度比较低的受主或施主杂质,就可以改变n或P沟道MOS场效应晶体管的阈电压并可控制在一个相当大的范围内40,41。是对集成电路中所有器件的有源沟道区进行离子注入,或者是利用附加的光刻工序来选择结构中的部分器件进行离子注入,这要视具体的应用而定。后一技术已表明能够在同一单片上做出带有增强态有源开关器件的耗尽态MOS负载元件,所得到的集成电路,其特征是功耗较低,开关速度较高,封装密度较大,而且能够在通常用以驱动双极型集成电路的低电压下(0到+5伏)进行工作41。

再次参考由(2.44)给出的MOS场效应晶体管阈电压的一般方程,就不难看出,如果将数量受到控制的与存在于硅衬底中的杂质同型或反型的杂质分别注入将漏扩散区和源扩散区隔开的区域的硅表面,则阈电压将分别得到恒增或恒减的结果。一旦注入完成,需要用高温退火的方法使杂质电活化,这样就可以增加或减少表面耗尽区内单位面积最大电荷密度,同时可以相应地改变器件的阈电压。应该记住,在注入完成之后,有源沟道区内表面附近有效杂质掺杂浓度不再是均匀的,并随进入硅的深度而变化,同注入的剖面及其后的高温处理过程中杂质的再分布有关。

离子注入工序平常是贯穿厚度通常为1000埃的二氧化硅薄绝缘层进行的,以防止表面污染42。绝缘物实用厚度范围,在低端受到针孔密度增加的限制,在高端则受注入层特性和剖面在各次制造中无法重现的限制。

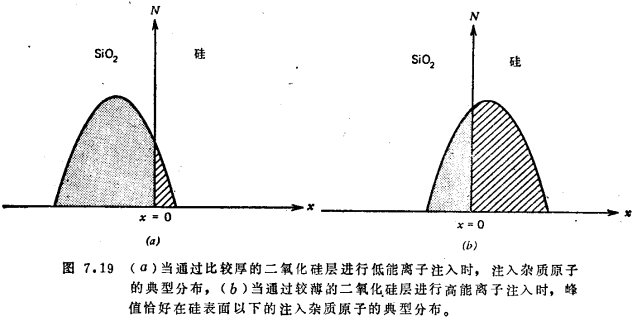

当用单能离子向无定形材料注入时,浓度剖面是峰值在表面以下距离为Rp处(平均入射距离)的高斯曲线。分布宽度由平均标准偏差ΔRp表征。当入射离子能量增加时,Rp和ΔRp也增加40。当采用低能离子贯穿比较厚的绝缘层进行注入时,在表面杂质浓度剖面上观测到的不可再现性往往是直接由于:在这样的条件下,注入离子的分布峰值,如图7.19(a)所示,是在绝缘物内,而不是在硅内。因此,实际上只是分布曲线的“末尾部份”留在硅内,而且绝缘层厚度或者入射离子能量的变化即使很小,也能使注入杂质分布曲线的末尾部份产生值得注意的变化。另一方面,如图7.19(b)所示,如果减小绝缘层的厚度或者增加注入离子的能量,注入离子分布曲线的峰值恰好在硅表面以下,而且在这样的条件下,绝缘层厚度或者离子能量小的变化对注入层的特性不会产生同样大的影响。

迪尔(Dill)和科朋(Coppen)43发现,如果将70千电子伏的硼离子穿过二氧化硅层注入到硅衬底,只要二氧化硅薄膜的厚度在500到1,500埃的范围以内,那么氧化物厚度较大的变化,只会引起注入层表面电阻率观测值较小的变化。不过,他们发现,当薄膜厚度超过1,500埃时,表面电阻率就有相当大的变化,因为比较大的一部分注入离子根本不能到达硅,而只停留在二氧化硅覆盖层上。

实际注入到硅表面的杂质量是随剂量(单位面积入射离子数)、离子能量和二氧化硅层厚度而变化的。在应用中,如需要将栅极氧化物层厚度约为1000埃的MOS场效应晶体管的阈电压改变大约几伏,通常用注入能量为15到50千电子伏之间的磷或硼杂质注入有源沟道区43。

利用低能离子注入技术来改变MOS场效应晶体管的阈电压的最为重要的应用,可以说是制作具有增强型的有源MOS场效应晶体管和具有耗尽型负载元件的大规模集成电路。通过采用普通的制作技术这是不难做到的,在栅极绝缘层形成之后,立刻在硅片上涂敷光致抗蚀剂,然后曝光,显影,这样,光致抗蚀剂就只留在所选择的地方,以掩蔽特定器件的有源沟道区,使其不受接着进行的离子注入的影响。其沟道区没有光致抗蚀剂覆盖层保护的器件,其阈电压将因注入而发生移动。在注入工序完成之后,除去保留下来的那部分光致抗蚀剂,再次用普通的工艺技术即可完成器件的制作。

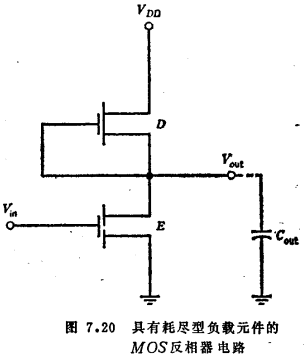

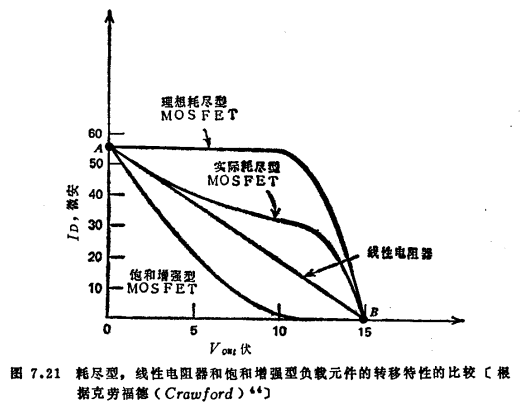

在同一个单片硅结构上同时获得增强型和耗尽型MOS场效应晶体管特性的优点可以从图7.20和7.21看出44。图7.20表示一个由增强型有源开关器件和栅源共接的耗尽型负载元件组成的MOS反相器。如果对反相器的输入使增强型器件初始处于“通”,而输出近似等于零伏,当输入改变为零伏时,增强型器件就变为“断”,耗尽型器件对输出端的电容负载必将充电到Vout=VDD。由图7.21可见,由于(理想)耗尽型负载元开关周期内,当输出从A移到B时,同类似的饱和增强型负载结构相比,(理想)耗尽型负载元件可以提供更大的随时间而变的电流。因此,电容性负载充电也较快。当然这也使开关速度加快。此外,采用耗尽型负载元件允许输出一直摆动到电源电压VDD。

图7.20所示的反相器中,耗尽型器件的源电极电势在作开关运用时,当然相对于固定衬底电势而变化。于是由此可知,源体效应有助于提高负载晶体管的夹断电压,而使电容充电时流经此处的饱和漏电流减小。这就使开关速度稍有下降。然而,尽管有这种影响,从图7.21曲线可以看得很清楚,实用的耗尽型负载元件远优于饱和增强型负载。甚至比线性电阻负载还要好。(在大规模集成电路中,应用线性电阻器负载元件,从制作工艺观点来看是不实际的,因为需要相当高的阻抗,这就需要极大的面积,而绝大多数的MOS工艺技术只能提供比较低的表面电阻率。)如果在反相器结构中应用栅漏电极共接的饱和增强型负载元件,在下面的器件断开以后,这个负载元件最初能够提供同样大的电流使电容器充电。然而,一旦电容器开始充电,Vout即开始上升,负载器件的栅源电压将下降,使充电电流大为减小,从而使完成开关动作所需时间增加。如同(非理想)耗尽型负载元件的情况一样,在Vout上升时,源体效应也同样使充电电流进一步减小。最后,应该注意,与耗尽型负载不同,如果栅-漏电极共接的增强型器件用作负载元件,反相器输出充电不能充到同电源电压一样。

采用具有增强型开关晶体管的离子注入耗尽型负载元件的许多优点,对于n沟道和p沟道MOS技术是很有用的,普通结构和自对准结构都能实现这些优点45,46。这样的技术经常用来制作单片计算机逻辑系统,随机存取存储器和只读存储器以及多种类型的非标准随机逻辑电路。

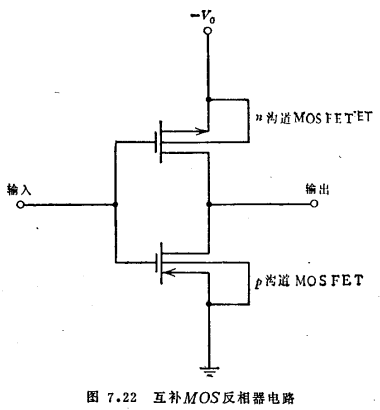

采用离子注入技术来控制MOS场效应晶体管的阈电压其它方面的应用是制作互补集成电路。旺拉斯(Wanlass)和萨氏(Sah)47首次提出:如果增强型n沟道MOS场效应晶体管与增强型p沟道MOS场效应晶体管共栅极串联连接,如图7.22所示,这种合成的结构具有简单反相器的功能,只要反相器处在其两种稳态中的某一状态,实际上几乎没有功耗。考察如图所示的互补反相器电路,所用逻辑信号是零和-V0伏。相对于各自的源区而言,增强型P沟道器件具有负阈电压,而增强型n沟道器件则具有正阈电压,由此可知,将零伏信号外加到公共的输入端,将同时使P沟道晶体管截止,n沟道晶体管导通。在这种状态下,实际上所有偏置电压在此刻都降落在P沟道MOS场效应晶体管上,而输出则近似等于-V0伏。另一方面,-V0伏的输入电压将使n沟道器件翻转为截止,沟道器件翻转为导通。这时偏压将降落在n沟道晶体管上,输出近似为零伏。在上述两种稳定的条件下,都有一个MOS场效应晶体管处于阻抗非常高的截止状态;因此,两个器件的串联几乎没有稳态电流。此外,由于MOS结构具有极高的栅极输入阻抗,在稳态条件下,栅极回路内没有电流。因此,不难看出,的确,互补MOS反相器在稳态时,实际上没有功率消耗。只有从某一状态转换到另一状态时,才有功率消耗。

图7.22所示的反相器电路是互补MOS逻辑的基本电路,也是目前正在生产的即使是最复杂的互补MOS大规模集成阵列的基本结构单元。除了“储备”功率消耗极低之外,互补MOS反相器的特点还有非常高的开关速度和在电源电压较大范围内具有非常高的抗扰性。与单沟道器件比较具有较高的速度是由电路的推挽运用实现的。从一种状态转换到另一状态时,输出电容总是通过已经转换到低阻抗状态的全导通MOS场效应晶体管来充电或放电。比较高的抗扰性是反相器具有对称的结构,各个器件具有非常高的断路电阻对导通电阻之比以及在过渡区具有极高增益的直接结果48。

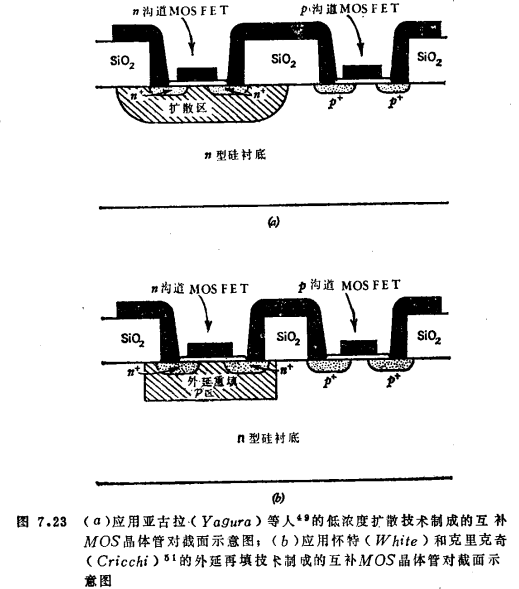

不久结果很明显,为了充分利用上述互补MOS反相器结构的特性,从而制出复杂的高速度,低功耗大规模数字集成电路,这就必须使能够在一块单独的硅衬底上制做出n和P沟道增强型MOS场效应晶体管的技术达到完善。要做到这点又需要在一块硅片表面上的特定区域形成轻掺杂的n和P型区;接着在轻掺杂的P型区构成n沟道MOS场效应晶体管,在轻掺杂n型区构成P沟道MOS场效应晶体管。参见第二章,特别是图2.12和2.17,不难看出栅极氧化物厚度和固定正界面电荷密度取典型数值,制作阈电压恒在1~3伏范围内重现,匹配良好的互补增强型MOS场效应晶体管结构,需要将轻掺杂P和n区的表面掺杂浓度精确地控制在近似等于1016/厘米3的数量级。要做到这一点起初是极端困难的,但是后来发现了几种技术,取得了成功。亚古拉(Yagura)、卡特林(Catlin)和赫琴森(Hutchenson)49应用低浓度扩散技术,能够在n型硅片内产生足够的轻掺杂p型区或者“阱”。然后,特性良好的n和P沟道增强型MOS场效应晶体管就是在极性相反的导电区内构成的,如图7.23(a)所示。其后阿塔纳斯(Athanas)50及其它人也提出了类似的技术。怀特(White)和克里克奇(Cricchi)51利用另外的方法在一块硅衬底上制成了相互匹配的互补MOS晶体管。他们的技术的主要根据是将n型硅片表面腐蚀成深沟,然后用轻掺杂P型硅外延地再填补这些深沟。再经过一系列的机械研磨和抛光过程,使硅片表面光洁平整,在硅片内极性相反的电导区中构成了如图7.23(b)所示的互补器件。这种制作方法一般并不理想,因为机械研磨与抛光工序比较困难;虽然如此伯吉斯(Burgess)和丹尼尔(Daniels)52应用类似的技术制成了低阈电压硅栅互补MOS集成电路。

随着离子注入工艺的最新发展,很明显,在一块单独的衬底上制作互补MOS器件需要的极性相反的电导区域还要通过离子注入工艺来实现,同时对注入区表面掺杂浓度进行控制所能达到的精度远远超过低浓度扩散或外延再填技术,从而导致对阈电压进行更好的控制。42,43作为用来说明采用离子注入工艺制作互补MOS结构达到高精度的例子。是科朋(Coppen)、奥布肯(Aubuchon)、鲍尔(Bauer)和莫耶(Moyer)53描述的一种制作用于电子手表的互补MOS集成电路的技术,电路用单节电池工作,电压为+1.2~+1.6伏。采用硼杂质离子注入法能够精确地控制构成n沟道器件的P区或“阱”的掺杂浓度,并将P沟道MOS场效应晶体管的阈电压降低到要求的数值。应用这一方法,阈电压始终能控制在0.6±0.3伏以内。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助