电子技术论坛

信息来源: 时间:2021-12-22

解析利用离子注入技术制作自对准栅极MOS管和集成电路

钼栅和硅栅结构都是依靠栅电极本身作为势垒,以阻挡杂质对MOS场效应晶体管有源沟道区的扩散。然而,假如采用扩散和离子注入的综合技术来构成漏区和源区,利用栅电极作为掩模以保护下面的沟道区在注入过程中免受高能杂质离子的辐射,就可以制出自对准MOS场效应晶体管结构。用此方法制作的分立器件和集成电路的寄生栅-漏和栅-源电容极小,实际上远远小于钼栅或硅栅器件。

应用离子注入技术制作自对准栅极的MOS场效应晶体管是由鲍尔(Bower)和迪尔(Dill)首先提出的26。虽然这些早期器件全部漏区和源区都是用单一的操作即用高能硼离子轰击硅片而构成的,由于离子注入区表面电阻率高,带来了令人讨厌的大的源区和漏区寄生电阻,并且需要两个独立的金属化工序:一是在注入操作以前先构成栅极区,二是在离子轰击后做与注入区的接触。然而用扩散和离子注入的综合技术构成源区和漏区能大大地改善器件的性能,这一点很快就变得很明显,而且只用一道金属化工序26,35。从制造产生的结果发现可以直接用来实现高速自对准P沟道MOS集成电路36,37,如图7.16所示。

应用常规的厚氧化物铝栅P沟道制作技术,构成如图7.16(a)所示的结构,在制作时有意识地把栅电极置于扩散源区和漏区之间,与这两个区各相隔0.1到0.2密耳,而不是彼此重迭。接着,用高能硼离子轰击薄片。由于铝栅电极和互连区,以及厚二氧化硅区作为离子注入的掩模是同样有效的,因此硅片上只有覆盖着二氧化硅薄层而无其它保护的地方才会受到掺杂,以致于在这些地方离子才能穿透薄氧化物而进入紧贴在下面的硅表面。如图7.16(b)所示,栅电极与扩散P+区之间的硅区就有硼离子注入,这样就将漏区和源区铺伸到栅电极边缘而获得完全对准。

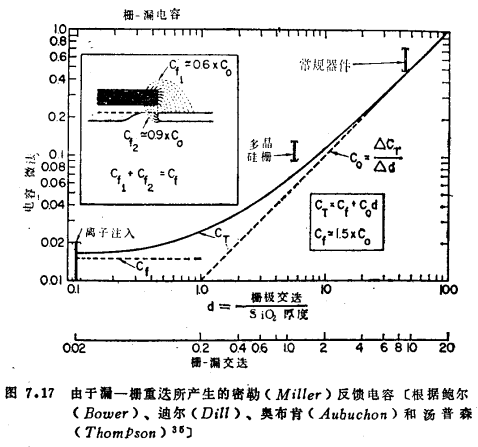

由于贯穿硅衬底的注入硼离子的横向运动极小,所以自对准离子注入MOS场效应晶体管的栅-漏和栅-源重迭量甚至比自对准硅栅或钼栅MOS场效应晶体管还小。后者漏区和源区的横向扩散对重迭电容的影响也相当大。这一点可以由图7.17说明,图上表明栅-漏负反馈电容或密勒(Miller)电容对栅-漏重迭量的依赖关系。下面的横坐标与厚度等于2000埃的栅极氧化物相对应。括以括号的短线表示普通(非自对准)MOS场效应晶体管和硅栅,以及离子注入器件实验测量值的范围。从实验数据不难看出,用离子注入技术来制作MOS场效应晶体管结构,其极间重迭可以达到极小的数值。

在离子注入工序完成以后,放在惰性气体环境中加温退火即可消除注入区内硅晶格的辐射损伤。退火温度越高,注入的硼原子变为电活性的受主比例就越大。不过,所允许的最高退火温度受到栅电极熔化温度的限制。对于铝栅器件退火温度大约为480~500°C,退火以后,注入P区表面电阻率的典型观测值约为3000欧姆/囗。

由于注入P区表面电阻率比较高,应使栅电极和扩散漏、源区之间的距离做得越小越好,它只受允许的掩模对准误差和P+区横向扩散的限制。因此,这种离子注入器件的尺寸仅稍大于普通MOS场效应晶体管器件,而注入区的寄生漏和源电阻可以保持很小的数值。例如,对于沟道宽度为10密耳,注入漏,源区各长0.1密耳的离子注入MOS场效应晶体管,假设注入硼区的表面电阻率大约为3,000欧姆/囗,则寄生漏区和源区电阻仅为30欧姆。这个附加电阻小于典型的沟道电阻值,因此,不会严重影响器件的增益。

另一方面,由于注入P区的表面电阻率较高,所以能够把高阻抗电阻器并入离子注入MOS场效应晶体管集成电路,而无需做额外的处理。37在所要求的部位注入电阻器,同时,以能达到自对准的要求来扩大各个晶体管的漏区和漏区。通过早先在扩散过程中构成的P+区接通电阻器。这些高阻抗电阻器可以用作反相级的负载元件,也可用来构成集成MOS数-模转换器的精确的电阻梯形网络。

利用离子注入技术能获得极小的栅-源和栅-漏电容值,这样就有可能制出高速MOS集成电路和高频分立MOS场效应晶体管。鲍尔(Bower)、莫耶(Moyer)和迪尔(Dill)36,37已经成功地制成速度超过10兆赫的P沟道离子注入MOS集成电路的移位寄存器和多路调制器。n沟道离子注入MOS器件对高频应用特别具有吸引力,因为电子迁移率高,可以带来较高的跨导。此外,不同于硼原子,当硅片在500℃退火时,注入的磷原子的大部分都能变成电活性的施主,因此注入n型区表面电阻率典型值约为300欧姆/囗。这样,与类似的P沟道器件比较,n沟道MOS场效应晶体管的离子注入区的寄生的漏区和源区电阻可以降低约一个数量级。

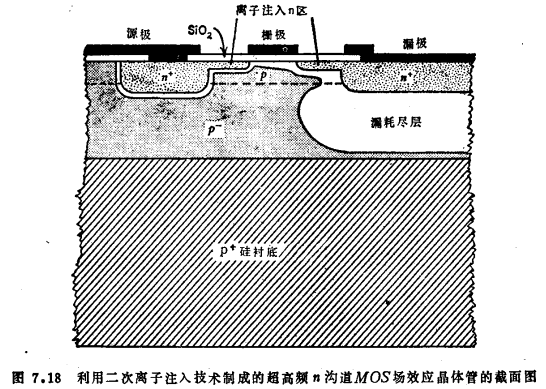

应用如图7.18所示的结构,香农(Shannon)、比尔(Beale)、斯蒂芬(Stephen)和弗里曼(Freemon)38,39采用两次独立的离子注入工序,做出了工作频率在千兆赫范围的分立n沟道超高频MOS场效应晶体管。在低电阻率P+衬底上生长的厚度大约为8微米的高电阻率(10欧姆-厘米)P型硅外延层用来将寄生漏-衬电容降低到最小,同时还可减小有效的漏-栅充电电阻。这些器件的栅极长度极小,平均约3微米,以得到高跨导的运用。然而,由于沟道长度较短和P型外延层电阻率比较高,如果不在金属化工序和其后为达到自对准效果的n型区注入之前,在沟道区内注入低浓度的P型层,这些器件就易被穿通。

如图7.18所示,P型注入层的深度比扩散漏和源的“接触”区浅,但是比磷注入时所构成的结要深。由第一次注入而在硅表面形成的低电阻率P型层可以起到阻挡漏极耗尽区扩展的作用,因此,在饱和漏极电流的工作条件下,能够防止穿通和维持MOS场效应晶体管的高输出阻抗。同样地,在沟道区内由于P型注入而出现较高的受主掺杂浓度,据观测,器件只工作在增强态时,所显示的典型阀电压值约为+1.5伏39。如上所述,在注入阶段产生的辐射损伤,可在惰性气体环境中和温度大约为500℃的条件下,进行退火加以消除。应用上述方法制作的典型器件在1千兆赫时,增益为4分贝,最大工作频率约为1.4千兆赫。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助