电子技术论坛

信息来源: 时间:2021-12-15

载流子迁移率随外加栅极电压的变化对MOS管电特性的影响

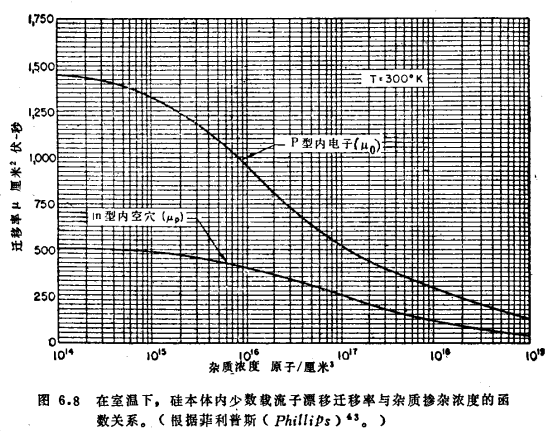

由于(6.4)式内有附加表面散射项,发现穿过MOS场效应晶体管的沟道区的载流子迁移率比半导体本体内的迁移率要低。(在室温下硅本体内电子和空穴迁移率的数值作为衬底掺杂浓度的函数已由菲利普斯(Phillips)43作出如图6.8的图表。)如前节所讨论的,随着栅极电压的增加,载流子的有效迁移率进一步下降。在Vc值低时,迁移率下降非常小,但是当栅极电压数值增加时,影响迅速增长44-48。

必须记住:在第四章中推导的描写MOS场效应晶体管作为外加栅压函数的漏极电流-漏极电压特性的方程是假设沟道内载流子迁移率等于常数时推导的。为了在栅压取较高数值时,使得这一方程同器件的实验观测特性取得更好的一致,我们只要采用经验决定的迁移率和栅极电压之间关系来代替取常数值的假设45。

里奇曼(Richman)47所提出的报告指出:当MOS场效应晶体管工作在外加漏-源电压较低而且远远低于夹断点时,载流子迁移率随外加栅极电压而变化的影响连同漏区或源区电路内可能存在的寄生电阻的影响特别显著。参考图6.9,该图表示典型的n沟道MOS场效应晶体管作为外加栅压函数的漏极电流-漏极电压的特性曲线。如果漏电流ID2和ID1是在漏电压保持常数,分别在不同的外加栅极电压值VD2和VD1时测量的,那么,对于足够小的VD而使器件在远低于夹断点以下工作时,应有

和

从(6.5)减去(6.6)得到

必须注意,假如在(6.5)和(6.6)中对于夹断点以下的漏极电流采取如由(4.14)给出的更精确的形式,将得到同样精确的结果。

VG2和VG1任意选择的(因此ID2和ID1也是如此)。因此(6.7)预计,对于栅极电压给定的变化,漏极电流就有相应的变化,而与栅极电压的初始值无关。换言之,(6.7)预计:当器件在夹断点以下工作,而漏极电压取固定值时,对于所有大小不同的电流,器件跨导为一常数。然而,可以看到,在栅极电压数值很大时,这个预计便不能成立。

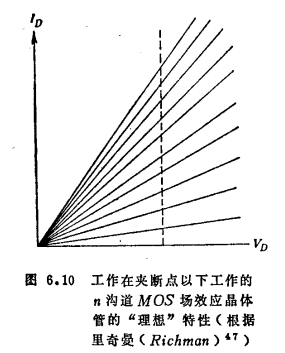

方程(6.7)预计,对于典型的MOS场效应晶体管,如果栅极电压减阈电压从1伏增到2伏而漏极电压保持恒定并远低于夹断点时,漏电流增加100微安,当栅极电压减阈电压再次上升,例如从9伏增加到10伏时,漏极电流仍然增加100微安。换言之,当相同的比栅极电压增加时,漏电流将保持以率增加,如图6.10所示。

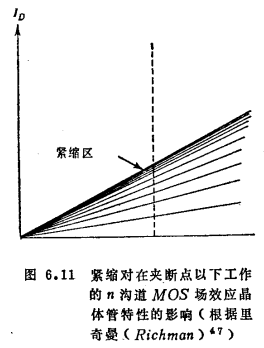

因此,对于非常高的栅极电压(但仍低于栅极介质层击穿电压),工作于夹断点以下的典型的MOS场效应晶体管的漏-源电阻可能趋近于零。但是由于两个原因,这样情况并不能发生。首先,如前面讨论过的,沟道内载流子的迁移率随栅极电压的增加开始减小,结果器件的跨导随栅极电压的而下降。其次,在漏区和源区之间将总是观测到最小的串联电阻。这是由于扩散的漏区和源区以及这两个区的金属接触,器件的焊接垫片与外壳引线之间的连接线等寄生电阻所产生的。因此,由于与栅极电场有关的迁移率和漏源电路内寄生串联电阻的影响,人们期望,在远低于夹断点以下工作的MOS场效晶体管的漏-源电导,在器件外加栅极电压很高时接近于一个极限值,在此条件下,电流对电压的特性就会“紧缩”如图6.11所示。

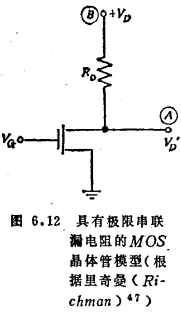

虽然上面讨论的两种机理,即与栅极电场有关的迁移率或串联寄生电阻,究竟哪一种是主要的,要依不同的MOS器件各自的特性而定,图6.12所示的简单电阻模型可以用来准确地描述上述一种或两种机理,对在夹断点以下工作的器件的电特性的影响47。如图所示,阻值为Ro的电阻同理想MOS晶体管的漏电极串联,这样的器件在夹断前的i-v特性由(4.14)给出。如果器件是用中等高电阻率p型硅衬底制作的并假设做得使表面耗尽区内的电荷影响比较小,那么,在A点n沟道MOS场效应晶体管的漏极电流近似等于

在模型中,非理想晶体管的实际漏电极在B点。漏极电流ID同样要流经串联电阻Ro,因此

将(6.9)代入(6.8)得到

假定,IDRo项与漏极电压VD相比较小,因此,(ID·Ro)与其它项相比可以忽略,(6.10)简化成

因此

或

方程(6.13)可以用来描述采用较大的外加栅极电压工作的n沟道MOS场效应晶体管的电流-电压的特性。(应用同样的方式,可以得出p沟道器件的类似的表达式。)在此条件下,只要简单测量所要研究的器件的特性便能决定Ro的实际值。不难看出(6.13)给出了正确的关系,因为在外加栅极电压足够低不致发生紧缩的极限情况下

(6.13)简化为(4.14)的形式(请注意,表面耗尽区的电荷影响已假定可以忽略不计)。另一方面,对于栅极电压足够高以致观测到明显的紧缩这时有

和

在这样的条件下,(6.13)分母中的第二项是主要因素,而且漏极电流接近于因存在着串联电阻Ro而产生的极限情况,亦即,在栅极电压减阈值电压取值较大时

可以看出在这样的条件下,理想的MOS晶体管本质上是短路状态,器件在夹断点以下的漏-源电流对电压的特性是由有效串联电阻支配的。

里奇曼(Richman)提出了描述依赖于栅极电场的迁移率与寄生串联电阻的模型,而(6.13)所预计的特性,经伦斯曼(Lunsmann)证明,它与测量典型的MOS器件所得到的实验数据取得了完全一致48。

正如MOS场效应晶体管在远低于夹断的低漏极电压工作时那样,在高栅极电压作用下,迁移率减小的效应和漏一源电路中的寄生电阻对于在饱和漏极电流区工作的器件的电特性会产生相当可观的影响。特别是对于如方程(4.41)所示的在夹断点以上的漏极电流对栅极电压减阀电压的平方的依赖关系,上述两种机理都要对这个平方律的使用范围有所限制。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助