电子技术论坛

信息来源: 时间:2021-11-9

MOS定时脉冲发生电路的构成方法及特性方程解析

台式电子计算机主要是串行同步式计算机,其中不可缺少的定时脉冲发生电路是规定信息流动的时间位置,对计算机进行时间分配的电路,它用来控制运算、存贮、显示等的驱动。换句话说,是构成计算机的中枢电路。此种电路以振荡器发生的方波脉冲作为信号源,确定时间位置的时钟脉冲![]() ,表示二进制数的位的t1、t2、t4、t8,表示十进制数n位的

,表示二进制数的位的t1、t2、t4、t8,表示十进制数n位的![]() 、

、![]() 、

、![]() ……

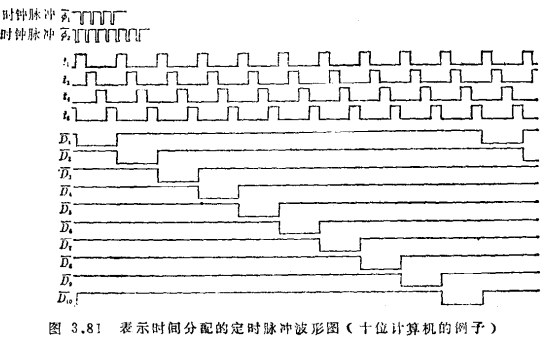

……![]() 等是其产生的输出信号。MOS定时脉冲电路。图3.81给出计算机时间分配定时脉冲的一种波形图。此电路用MOS场效应晶体管集成电路化时,可以有下述结构。

等是其产生的输出信号。MOS定时脉冲电路。图3.81给出计算机时间分配定时脉冲的一种波形图。此电路用MOS场效应晶体管集成电路化时,可以有下述结构。

应该将哪一个电路进行集成化,这取决于设计的难易,芯片尺寸的大小,所用单元电路的特性等,这里不详细叙述,只讲一下定时脉冲电路的构成方法。

(1)采用触发器电路的定时脉冲发生电路

现有的触发器之中以J-K触发器最为常见,具有便于使用的特点。J-K触发器的真值表如表3.12所示。用此种J-K触发器可实现特性相当良好的电路结构。现在考虑十位计算机中用J-K触发器构成的表示十进制数的定时脉冲发生电路。所要求的输出状态S有10个,要得到这么多的输出,所需的J-K触发器数目n为20)

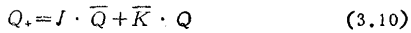

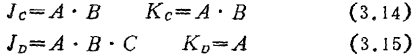

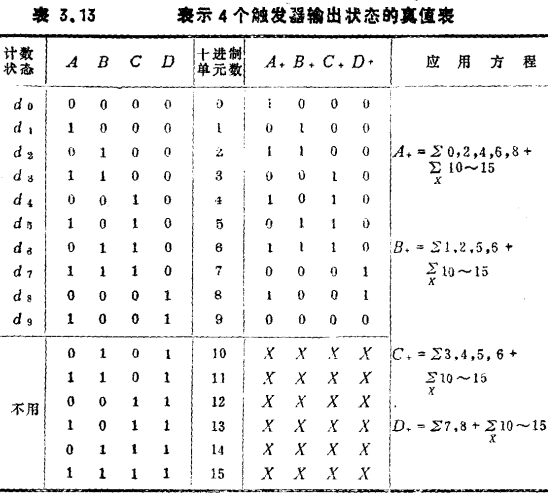

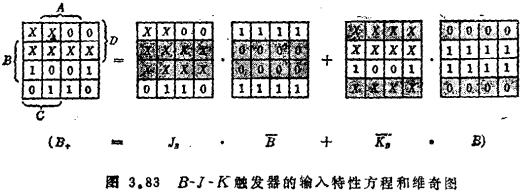

由上式得知n≥4。也就是说,用四个触发器可得到表示十位的脉冲。MOS定时脉冲电路。今设表示十个状态的四个触发器输出状态为A、B、C、D,这些时间流图的汇总即为表3.13的真值表。t+1时刻的某触发器的状态决定于t时刻的触发器状态。从而可求得A-J-K触发器的输入特性方程20)21)。J-K触发器的输入特性方程为

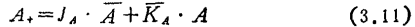

A-J K触发器有

同理,求C、D的J-K触发器输入特性方程,得

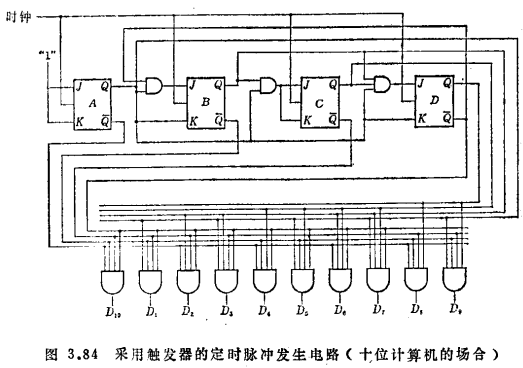

如上所述,由四个触发器的输入特性方程可推导出式(3.12)~(3.15),如将此结果直接构成电路,即得图3.84的电路。

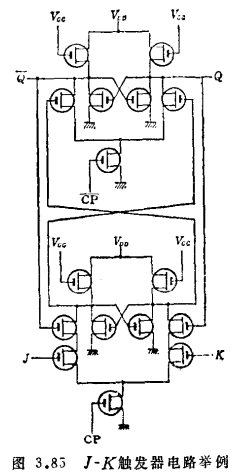

将此四个触发器电路的输出接到译码器,可得波形D1~D10(图3.81),用以表示所希望的十位计算机的十进制数。采用这种J-K触发器构成的定时脉冲发生电路,如图3.85所示,当然不仅限于此种电路。

以上只谈了十位计算机,这种电路也适用于11~16位的计算机。

总之,采用这种结构时,输出反馈信号线较多,且元件面积也大,增加了集成电路设计的复杂性,这是一个不可避免的缺点。

(2)使用移位寄存器的定时脉冲发生电路一一122)23)

移位寄存器通常具有将“1”电平状态或“0”电平状态循环存储于电路的能力。如用此种能力来代替触发器的存储能力,则能得到与前节所述的由触发器构成的定时脉冲发生电路有完全相同功能的电路。MOS定时脉冲电路。其结构是将移位寄存器用作存储电路,所以必须有循环的输出反馈电路。此种电路具有相当于一级存储的能力,为表示十位计算机的十进制数,移位寄存器数目应有10-1个。也就是说,对n位计算机而言,移位寄存器的数目S与输出反馈电路输入端数目I,有下述关系

如准备好满足上式的元件,即可构成所希望的定时脉冲发生电路。

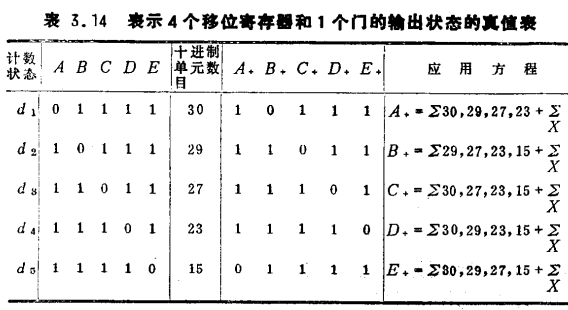

为了说明简单起见,现考虑表示五位计算机十进制数的定时脉冲发生电路。为表示五位数的五种状态,由式(3.16),得S=I=4,应准备移位寄存器四个,4输入端门一个。今设表示五种状态的四个移位寄存器及一个门的输出状态分别为A、B、C、D和E,将其时间流图也一并记入,可得表3.14的真值表。t+1时刻的某移位寄存器的状态由t时刻的移位寄存器状态决定。从而可求得A移位寄存器的输入特性方程20),21)。A移位寄存器输入特性方程与D型触发器的功能相同,所以有

考虑到A移位寄存器有

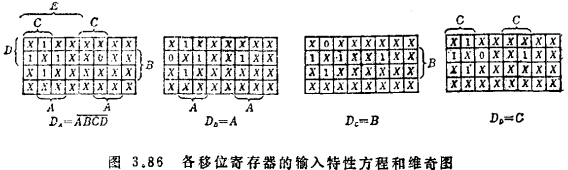

求解DA,图3.86的维奇图可写成移位寄存器的输入特性方程式。由此得到

同理,解B、C、D、E,得

此处,E为门的输出,输入特性方程可由表3.14按“与非”门的方式求得

此式与A移位寄存器的输入特性方程完全相同。即门E的输出端与A移位寄存器的输入端连接,意味着输出信号的反馈。

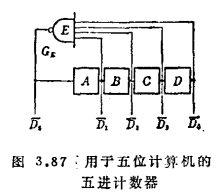

上面推导出四个移位寄存器和一个门的输入特性方程,将其结果直接化为电路即得图3.87的电路。采取这种电路构成时,只有在各移位寄存器的输出状态均为“1”电平(因用的是正逻辑,故为0V电平)时,门E的输出才为“0”电平(-EV)。此“0”电平在不同的时刻依次移动到各移位寄存器,当各移位寄存器不来这种“0”电平时,门的全部输入端为“1”电平,则门E的输出为“0”电平,重复这样的状态可得到所希望的定时脉冲波形(图3.81)。

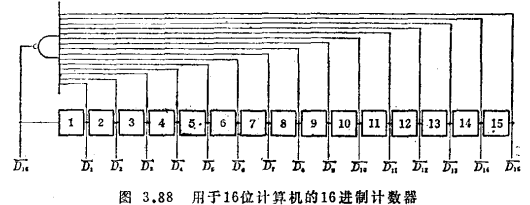

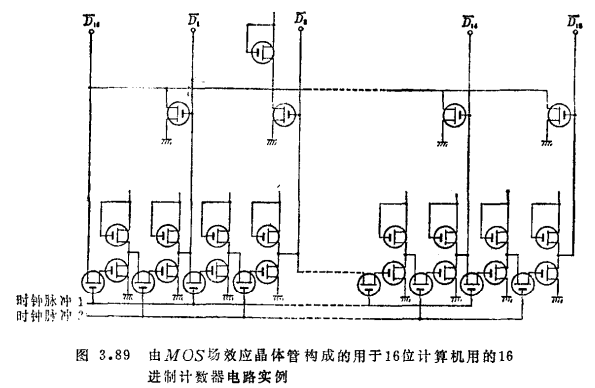

至此,为说明逻辑结构,我们介绍了表示五位计算机十进制数的定时年脉冲发生电路。可将此种电路结构加以扩展得到表示16位计算机16进制数的定时脉冲发生电路,如图3.88所示。图3.89是用MOS场效应晶体管作成的这种电路实例。

如上所述,用移位寄存器构成定时脉冲发生电路要比用触发器构成同样的电路容易得多,元件数也少,有可能实现充分满足所要求功能的电路。MOS定时脉冲电路。然而这种构成也与上节一样,输出信号反馈线数目多,对n位计算机来说,需要n-1条输出信号反馈线及n-1个输入门。所以对集成电路设计来说,这种电路结构并不一定是尽是优越的电路。

(3)使用移位寄存器的定时脉冲发生电路一2

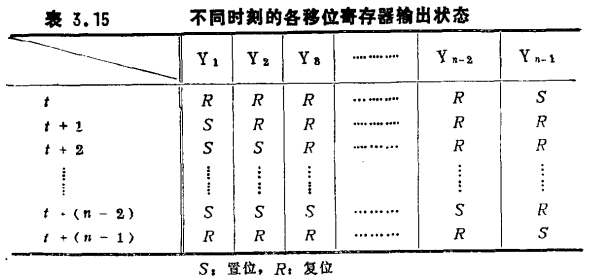

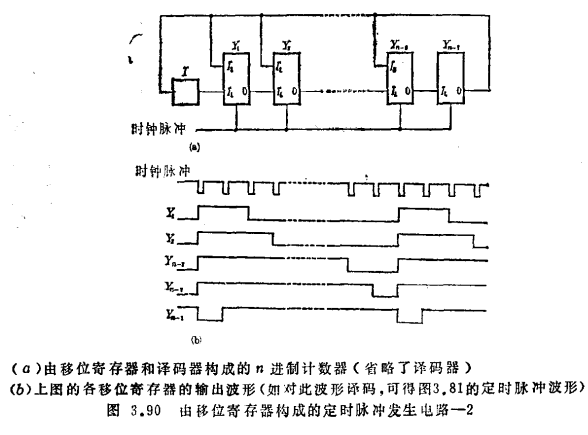

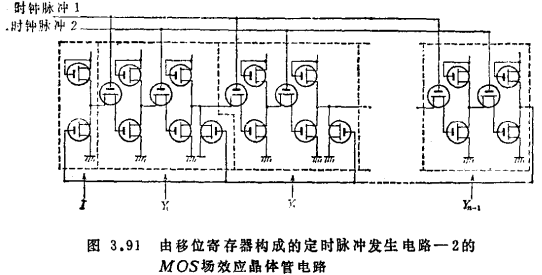

与上节完全一样,可用移位寄存器构成另一种定时脉冲发生电路。移位寄存器的循环或存储“1”电平及“0”电平的能力可用触发器电路来代替,这一点与上一节一样,n位计算机的定时脉冲发生电路需用n-1个移位寄存器这一点也一样。但此时所用的移位寄存器和上一节的不一样,是由有强制复位功能的n-1个移位寄存器Y级联而成。该电路末级Vn-1的输出信号反馈到各级移位寄存器的复位输入端以及初级移位寄存器的输入端;只有在末级移位寄存器Yn-1置位时,各移位寄存器才复位。这是本电路的特点。在某时刻t,若末级移位寄存器Vn-1置位,则各移位寄存器复位;至t+1时刻,只有Y1置位,其它移位寄存器Y2~Vn-1持续t时刻的复位状态。至t+2时刻,Y1的置位状态传输到Y2,Y1、Y2均置位。其它移位寄存器Y3~Yn-1依次持续前一时刻t+1的复位状态。同理,只有Y1、Y2、Y3置位时,其它移位寄存器全部复位;至t+(n-1)时刻,置位状态移至Yn-1,在Yn-1置位的同时,Y1~Yn-2全部被复位,回到初始状态。表3.15是表示这种状态的表。此种电路结构,是把置位状态经一定时间逐次地向后一级传递的,所以如其输出按各自的延时序列被译码,即可得所希望的表示n位计算机十进制数的波形。图3.90、图3.91分别为上例的逻辑电路和具体电路。

本例的输出信号反馈线只有1条,所占布线面积极小,如认为译码器也是各移位寄存器结构的一部分,可构成相当简单的电路。但由于有译码器,元件数稍多一点,这是它的缺点。

如上所述,定时脉冲发生电路是多种多样的,应从电路特性和电路设计方面研究何种形式最能满足要求,要采用最方便的形式进行高密度集成电路化。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助