电子技术论坛

信息来源: 时间:2021-11-8

MOS存储器阵列及其MOS存储器是如何构成电路图分析

本节将要叙述实际存储器如何构成。在构成存储器时,外围电路有使用MOS电路和使用双极型电路的两种情形,本节只讲使用MOS电路的情形。

(1)MOS存储器

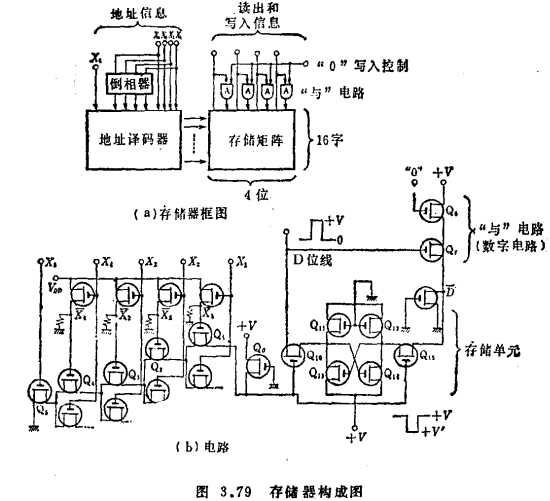

由于MOS电路容易集成并且功耗低,如充分利用这些特点即可在单片上制造全部存储单元和外围电路。从这种意义上来说,希望对MOS存储单元使用MOS外围电路。但考虑到速度等因素时,MOS外围电路就不一定能充分满足要求。图3.79(a)是用447个P沟道MOS晶体管构成的16字×4位的MOS存储器框图,图3.79(b)是它的电路图。

用于选通地址时,同5输入端“与”电路的方式相比,采用树枝形地址译码器可减少元件数目。这种译码器有16个输出功能,譬如,当X1~X4全部为+V时,Q1~Q4全部导通,所以可选择一个地址,存储单元的地址线电位从+V(+18V)变到+10V。为了保证非选通状态下的地址线的电位为+V,Qo被接入。存储单元部分是上节已经讲过的,在写入二值信息的“0”信息时,位线![]() 万由Q6、Q7的“与”电路驱动。写入“1”时在位线D上加正向脉冲。Q8的器作用是使位线万的电位复原。此存储的周期为2~3μs。MOS存储器阵列。

万由Q6、Q7的“与”电路驱动。写入“1”时在位线D上加正向脉冲。Q8的器作用是使位线万的电位复原。此存储的周期为2~3μs。MOS存储器阵列。

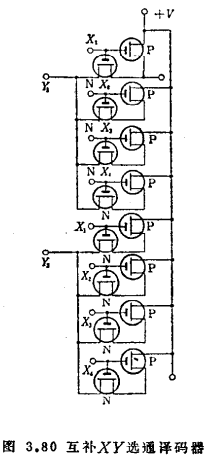

用互补型存储单元构成存储器时也完全一样。16字×4位的存储器的结构如图3.79(a)的框图所示,64个存储单元及其外围电路均由MOS晶体管构成。MOS存储器阵列。图3.80是16字的XY选通地址译码器,由32个MOS晶体管构成。如选通一个X信号和一个Y信号,则16个N型晶体管中只有一个导通,且信号被译码。此译码器可在存取时间50ns,写入时间75ns的速度下工作。

以上是既包括MOS存储单元、也包括外围电路,全部用MOS管构成的情形。为了提高外围电路的速度,外围电路改用双极型晶体管构成,而存储单元部分仍用MOS管制作,以提高集成度。在这种场合,为使性质不同的两种电路组合起来,一定要用多片方式。例如,采取128字×64位P沟道MOS存储单元时,可在读出周期为35ns,写入周期为60ns的速度下工作。

(2)相联存储

相联存储的应用领域因容量而异。大容量相联存储器虽也能用作主存储器,但现有产品多为小容量的,下面介绍小容量存储器的应用。

首先是用作函数表。对应于变数X求函数f(x)时,如将f(x)编制成表存储起来,一经询问到x的比特位置,就能很容易求得f(x)值。

其次,在时间分割的计算机中,将连续的地址存入预定大小的存储范围,并将其处理成页面,作为页面地址方式使用。这样可使主存储装置得到有效的利用。

再就是供情报检索之用。与表现有情报特点的询问情报联系起来,抽出所希望得到的情报。

除上述的应用领域之外,今后还会更广泛地用作各种函数表或主存储器的辅助装置,但很难用作大容量的外存储器。MOS存储器阵列。从速度方面来看,存储单元应以使用MOS为主,而外围电路应以使用双极型为主

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助