电子技术论坛

信息来源: 时间:2021-11-4

MOS移位寄存器的种类(静态型、动态型、 多相时钟)详解

MOS移位寄存器大体上可分为静态静型和动态型两种。态型移位寄存器过去由双极型集成电路等构成的J-K触发器组成。动态型主要利用MOS集成电路特有的栅电容暂存信息的功能,属于用两相时钟转移信息的类型。除了用两相时钟移位外,为了降低功耗,也有增加时钟数目、用多相时钟转移信息的电路。这些电路的工作原理以后再说明。

(1)静态型移位寄存器

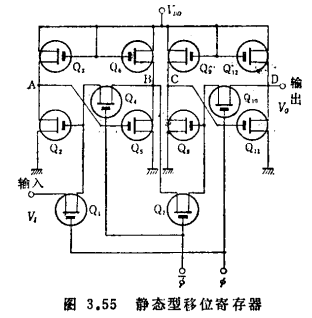

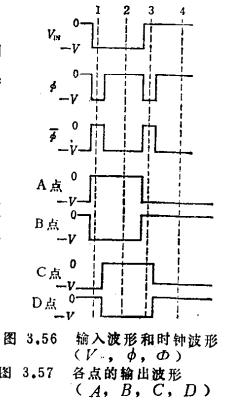

静态型移位寄存器典型的电路例子,如图3.55所示。首先说明此电路的工作原理。输入晶体管Q1藉助时钟脉冲Ф而通断,起传递输入信号的作用。时钟脉冲![]() 相位恰好相反。用两相时钟Ф1、Ф2代替和也能完成同样的动作,此处就前一种情形加以说明。

相位恰好相反。用两相时钟Ф1、Ф2代替和也能完成同样的动作,此处就前一种情形加以说明。

现在研究图3.56的状态1。输入信号为“1”电平的电位,时钟脉冲Ф为“1”电平,所以Q1导通,Q2的栅变为“1”电平的电位,Q2也导通。从而A点为“0”电平,Q5截止,B点为“1”电平。但由于![]() 是“0”电平,所以Q7截止,B点的信号不能传输到Q8。Ф为“1”电平时,Q10虽也导通,输出状态还是不变。接着在状态2,Q4 ,Q7导通,Q1、Q10截止。Q4导通,所以Q2的栅电位更加为“1”电平,A点维持在“0”电平。另一方面,由于Q7导通,B点的“1”电平传输到Q8的栅,使Q8导通,C点为“0”电平,所以输出端D点变为“1”电平。然后在状态3,输入信号为“0”电平,所以Q2的栅为“0”电平,Q2截止,A点为“1”电平,B点为“0”电平。C、D两点保持原来的状态。

是“0”电平,所以Q7截止,B点的信号不能传输到Q8。Ф为“1”电平时,Q10虽也导通,输出状态还是不变。接着在状态2,Q4 ,Q7导通,Q1、Q10截止。Q4导通,所以Q2的栅电位更加为“1”电平,A点维持在“0”电平。另一方面,由于Q7导通,B点的“1”电平传输到Q8的栅,使Q8导通,C点为“0”电平,所以输出端D点变为“1”电平。然后在状态3,输入信号为“0”电平,所以Q2的栅为“0”电平,Q2截止,A点为“1”电平,B点为“0”电平。C、D两点保持原来的状态。

在状态4时,Q4、Q7导通,Q1、Q10截止。此时因B点为“0”电平,所以Q8的栅变为“0”电平,Q8截止,C点变为“1”电平。因而Q11导通,输出端D点变为“0”电平。

于是,输入信号延迟1位传输到输出端。对使用两相时钟的情形,也可以作完全一样的说明。

如果取这种电路形式,1位需用元件数为12个。与后述动态型移位寄存器相比,元件数增加了一倍。从而,这种电路形式的位数不能增加许多,一般只作成4位,8位至20位的移位寄存器。这种移位寄存器输入有相移的脉冲![]() 也可以用。MOS移位寄存器。也就是说,可用作动态型移位寄存器。

也可以用。MOS移位寄存器。也就是说,可用作动态型移位寄存器。

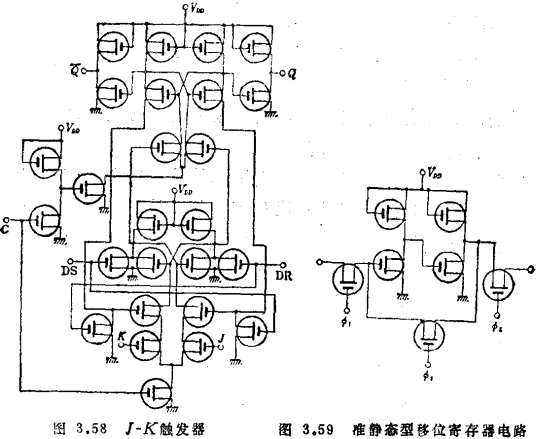

静态型移位寄存器也可用J-K触发器构成。例如可用图3.58的J-K触发器构成移位寄存器的一位。但由于元件数目多,谈不上有什么优点。我们认为,今后前一种电路的移位寄存器是静态型移位寄存器的主流。

这种电路的变种有准静态型电路。准静态型电路如图3.59所示(这种电路也可看作是下述动态型的变种)。这是一种通过Φ2加反馈使信号得以长期保持的电路。

(2)动态型移位寄存器

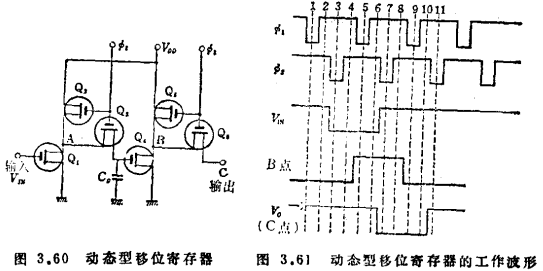

动态型移位寄存器与节(1)所述的静态型不同,是一种利用栅上可暂存信息的MOS特有功能而构成的移位寄存器。这种移位寄存器每一位只用6个晶体管,不难做出位数多的电路。基本电路如图3.60所示。现在我们看一看在输入端加图3.61所示的输入信号VIN,Φ1,Φ2有图示的关系时,一位的输出(C点)波形Vo如何。

在状态1,Φ1加“1”电平电位,所以晶体管Φ2、Φ3呈导通状态。但由于输入端信号零,“1”电平的电位传递到B点。MOS移位寄存器。Φ2上只输入“0”电平电位,所以Q5、Q8处于截止状态。从而,B点的“1”电平电位向Q4的栅电容Cg充电。

在状态2,Φ1、Φ2都是“0”电平电位,Q2、Q3、Q5、Q6均处于截止状态,因输入信号是是“0”电平,所以B点保持在状态1。

进入状态3时,Φ2处于“1”电平状态,Q5、Q6导通。从而Q4导通,在C点输出“0”电平电位。在这种状态下,输入端虽有“1”电平信号进入,但因Φ1处于“0”电平,输出不受影响。

状态4与状态2相同,Φ1、Φ2均为“0”电平电位,所以状态3得以保持。

进入状态5后,Φ1处于“1”电平电位,输入端也处于“1”电平电位,所以A点为“0”电平,充电于Q4栅上的电荷通过Q3、Q1放电,B点变为“0”电平。此时Φ2为“0”电平,所以C点仍保持以前的状态。

状态6是保持状态。进入状态7后,Φ1为“0”电平,Φ2变为“1”电平,所以Q5、Q6导通,但因Q4栅上的电荷全被放光,所以Q4截止,输出端C输出“1”电平。状态8是保持状态,进入状态9后,Φ1为“1”电平,Q2、Q3导通,但输入端处于“0”电平,所以B点呈“1”电平。由于Φ2为

“0”电平,C点仍保持状态7。

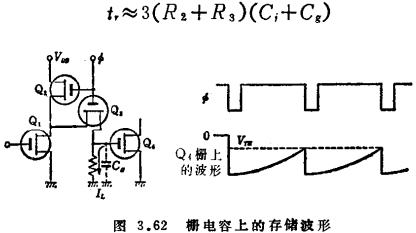

状态10是保持状态。进入状态11时,Φ1为“0”电平电位,Φ2为“1”电平电位,所以Q5、Q6导通,但由于B点为“1”电平,输出端C点变为“0”电平。将以上各状态概括起来,有图3.62的波形关系。

在状态1,当频率降低即进入Φ2的时间较长时,充电在Cg上的电荷,由于电荷Q4的栅与衬底间漏电而逐步衰减,使信号消失。因而,这类移位寄存器的工作频率有一个下限。MOS移位寄存器。漏电越小,工作频率的下限就越低。从定量的角度考虑,Q4栅上的电荷通过Q3漏泄掉,Q4的栅电压降至Q4的阈值电压(Vth)的时间可谓下限工作频率。简而言之,就是![]() 所决定的时间。假设漏电阻为R=1011Ω,常温下频率下限约为3Hz。MOS移位寄存器。然而,反向偏置P-N结的漏电以及氧化膜的表面态,都能使漏电发生变化。工艺条件的优劣也能使下限频率改变。

所决定的时间。假设漏电阻为R=1011Ω,常温下频率下限约为3Hz。MOS移位寄存器。然而,反向偏置P-N结的漏电以及氧化膜的表面态,都能使漏电发生变化。工艺条件的优劣也能使下限频率改变。

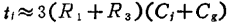

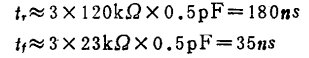

现在我们再来看看频率上限。由于通过导通的晶体管Q2、Q3向Q4的栅充电,假定Q2、Q3的导通电阻是线性的,设为R2、R3,则图3.63的上升时间tr为

由于Q4的栅电荷通过Q3、Q1放电,假定Q3、Q1的导通电阻是线性的,设为R3、R1,则下降时间为

两式中的Ci为P-N结电容,Cg为Q4的栅电容。

今设R2=100kΩ,R3=20kΩ,R1=3kΩ,Ci=0.2pF,Cg=0.3pF,则

由于是两相时钟脉冲,![]() 是上限频率。

是上限频率。

此频率上限与功耗也有关系。若增加每一位的功耗,即减少导通电阻时,就可以缩短上升和下降时间,提高频率上限。

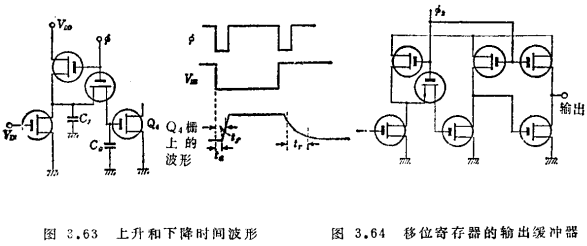

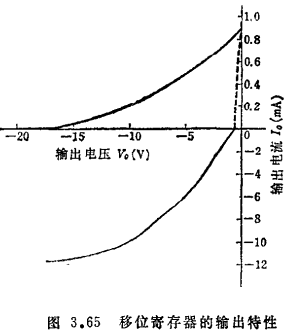

这类移位寄存器的输出级由缓冲器构成,便于与后续电路匹配。输出缓冲器的例子示于图3.64。举东芝公司生产的64位移位寄存器TM4105M为例,其输出电压和输出电流之间的关系如图3.65所示。根据这种特性可以做出与双极型电路连接的各种电路。

动态型移位寄存器只在加时钟脉冲时才有电流流过。从而可由脉冲宽度和占空因数来改变功耗。无论如何,与静态型移位寄存器相比,其功耗也是小的,这是它的特点。

(3)多相时钟移位寄存器

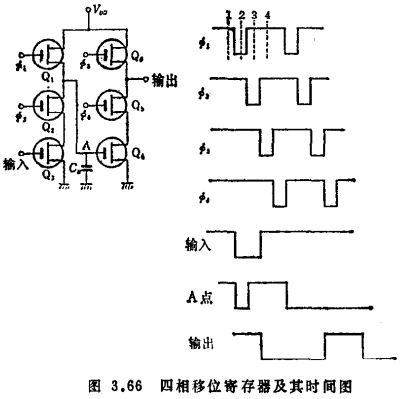

两相时钟的动态型移位寄存器已在第(2)节讲过。为了降低功耗、减小元件尺寸及提高成品率,可考虑三相、四相、六相时钟的移位寄存器。此处对最一般的四相时钟移位寄存器进行讨论。

图3.66给出四相时钟移位寄存器的基础一一寄存器的1位的电路。元件数是6个晶体管,与两相时钟的情形相同。MOS移位寄存器。我们看一看各时钟有图3.66的时间关系而输入信号又如图所示的情形。在状态1,全部时钟均为“0”电平,即使输入信号为“1”电平,也完全不影响输出状态。在状态2,若Φ1加“1”电平电位,则晶体管Q1导通,A点的Cg充电到VDD。此时,加输入信号,但Φ2为“0”电平,所以Q2截止,A点的电荷得以保持。

进入状态3时,Φ2加“1”电平电位,Q2导通。但由于其它时钟都是“0”电平,所以Q1、Q4、Q5、Q6截止。又由于Q3有输入信号,故Q3导通。结果,A点的电荷,在有时钟脉冲Φ2、有输入信号的时间内放电。当Φ3、Φ4均为“1”电平时也可作完全一样的考虑。结果,也可用四相时钟脉冲获得1位延时。

四相电路的速度比两相电路高四倍。下面对此进行计算。

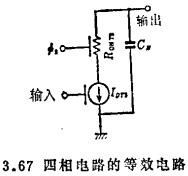

等效电路如图3.67所示。上升时间ton可近似写作![]()

![]() 。今设

。今设![]()

![]() ,则有

,则有

。算得下降时间toff约为13.65ns,短于上升时间ton,这就是预充电时间。因系四相电路,约需要56ns。MOS移位寄存器。这意味着可在18MHz的频率下工作。这比两相时要快得多。只在CN充放电时有功耗。从而功耗可按

。算得下降时间toff约为13.65ns,短于上升时间ton,这就是预充电时间。因系四相电路,约需要56ns。MOS移位寄存器。这意味着可在18MHz的频率下工作。这比两相时要快得多。只在CN充放电时有功耗。从而功耗可按![]() 结点=FCNVDD2进行计算。F是时钟频率。设频率为1MHz,则

结点=FCNVDD2进行计算。F是时钟频率。设频率为1MHz,则 结点=0.3×10-12×122×106=43.2μW。功耗比两相时小两个数量级。

结点=0.3×10-12×122×106=43.2μW。功耗比两相时小两个数量级。

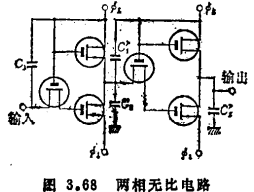

上面叙述了四相时钟移位寄存器的特性,如进一步巧妙地使用时钟脉冲,即可构成各种电路。两相无比电路是用两相脉冲使电容器充放电,用来传输信号的移位寄存器。图3.68就是这种两相电路。如适当选取电容器C1和C2的比值,晶体管Q1和Q2就可以采用同样尺寸(同样的gm)的元件。并且该电路只有电容器的充放电,没有直流电流流过,只流过过渡电流,所以功耗极低。

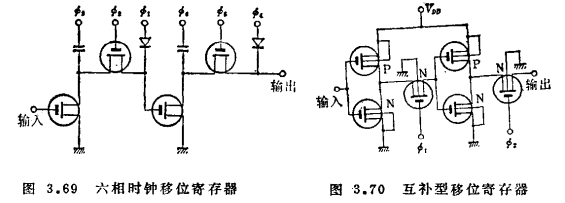

也有时钟数目更多的移位寄存器。六相移位寄存器的例子,如图3.69所示。增加时钟数目,将使时钟驱动等外围电路变得很复杂,所以除了降低功耗外,优点极少。

目前最常用的是两相有比电路和两相无比电路。

此外尚有使用互补电路的移位寄存器。在几种类型的互补移位寄存器。在几种类型的互补移位寄存器中,典型的例子如图3.70所示。其优点是能高速工作,低功耗等,这些优点是用单沟道构成的移位寄存器所不具备的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助