电子技术论坛

信息来源: 时间:2021-11-2

C-MOS(互补MOS)逻辑电路-输出入电压特性

C-MOS(互补MOS)逻辑电路

以上各节叙述了单一沟道(P沟道或N沟道)MOS晶体管逻辑电路。C-MOS逻辑电路。此处对P沟道和N沟道组成的C-MOS结构的逻辑电路加以说明。

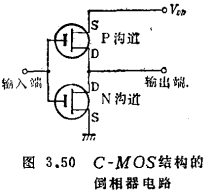

C-MOS的基本电路是倒相器电路,如图3.50所示。

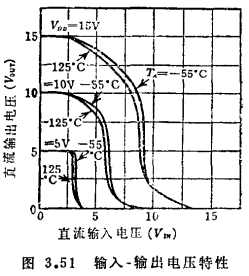

该电路中,将P沟道晶体管的漏与N沟道晶体管的漏接在一起作为输出端,将两个晶体管的栅接在一起作为输入端。并且在P沟道的源上加正电压,在N沟道的源上加负电压。若在输入端加电压,当Vin=0时,P沟道晶体管的VGS=-VDD,呈导通状态,N沟道的VGS=0,呈截止状态。从而输出电压大致上等于VDD。Vin=VDD时,P沟道和N沟道的工作状态与上述情形恰恰相反,P管截止而N管导通,输出电压为0。如上所述,用C-MOS时的逻辑摆幅范围为由0到VDD。翻转电压为电源电压的45~50%。C-MOS逻辑电路。图3.51给出C-MOS倒相器的特性。

由于输入阻抗极高,逻辑摆幅很大,并且翻转电压高达V-DD的45~50%,所以可得到高噪声容限的电路。

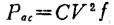

另外,C-MOS电路无论处于“1”还是“0”哪一种逻辑电平,总有一个起晶体管截止,所以无信号时,没有从电源流出。无信号时功耗仅取决于漏泄电流,其值为单沟道时的千分之一左右。工作时,来自电源的电流取决于负载电容C的充放电。因此,功耗可由下式表示。

式中,C为负载电容,V=VDD,f为工作频率。

在由“0”电平向“1”电平转换的期间,有一个两晶体管器均导通的转变点。此时,有瞬态脉冲电流自电源流入,产生功耗,但其值极小。图3.51输入-输出电压特性

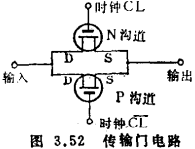

在C-MOS集成电路中,与倒相器电路同样被广泛应用的基本电路有信号传输门电路。

图3.52为其电路图。单门的MOS晶体管,在源-漏之间也具有双向性,其导通时的输出电压为输入电压减掉Vth(此处VG=VDD)。然而对于CMOS结构的传输门电路,通过对并联晶体管的两个栅分别加![]() ,则处于导通状态时,任一晶体管都完全导通,所以可得与输入电压完全相等的输出电压。

,则处于导通状态时,任一晶体管都完全导通,所以可得与输入电压完全相等的输出电压。

上述的倒相器电路和传输门电路组成的电路,有两输入端“或非”门和延迟型触发器电路。现在对这种电路加以说明。

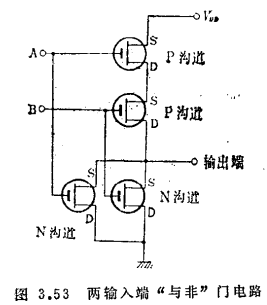

在图3.53,当两个输入端都为“0”电平时,串联的两个P沟道晶体管都导通,两个N沟道晶体管都截止,在输出端可得到电VDD。若其中任一个输入端变为“1”电平,则P沟道管截止,而N沟道管导通,所以输出电平翻转。也就是说,具有“或非”门特性。欲构成三输入端或四输入端N沟道“或非”门电路时,可按图3.53,将P沟道管串联,N沟道管并联,增加串并联管的数目即可。

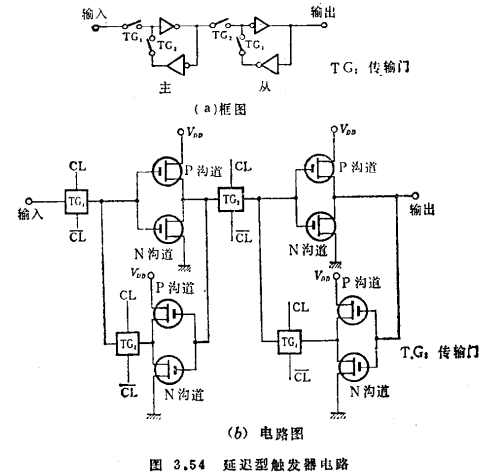

延迟型触发器(D型触发器)的框图和电路图如图3.54所示。由图(a)可知,整个电路由传输门电路7G1、TG2和倒相器电路组成。整个电路还可分割为主电路和从电路。

输入信号为低电平时,假设TG1导通,同时G2截止,则信号靠主触发器电路取样。接着,当TG2导通时,则信号由主电路传输到从电路,但同时又因TG1导通,所以信号仍静态保持在主电路内。C-MOS逻辑电路。从而在输出端可得到延迟1位的信号。