电子技术论坛

信息来源: 时间:2021-11-2

MOS集成电路多相时钟电路中的逻辑电路

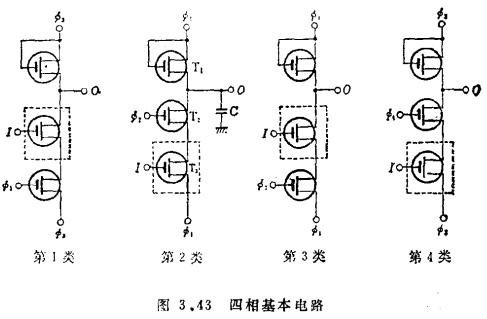

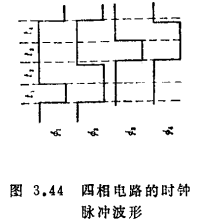

MOS集成电路多用两相时钟的电路方式,三相、四相等多相时钟电路也在进行研究。此处简单介绍大家最熟悉的多相时钟电路即四相时钟方式的逻辑电路。图3.43给出该电路的基本门电路,根据应加到端点的时钟信号可分为四类。图3.44表示出应加的时钟信号。在说明电路时,设所用的晶体管处于低电平L时为导通状态;处于高电平H时为截止状态。MOS集成多相时钟电路。现以图3.43的第二类电路为例进行说明。

在图3.44所示的时钟信号的t1时间内,第二类电路上加有时Ф1和Ф2,所以晶体管T1、T2导通,输出端电容C预充电到L。接着在t2时间内,时钟脉冲Ф1到H,晶体管T1截止而T2继续处于导通状态,于是根据晶体管T3的输入端是L电平还是H电平,输出端电位则变为H电平或继续处于L电平。

在t3和t4时间内,晶体管T1和T2截止,所以于t2时间确定的电平得以持续,可用作第三类、第四类的输入信号。

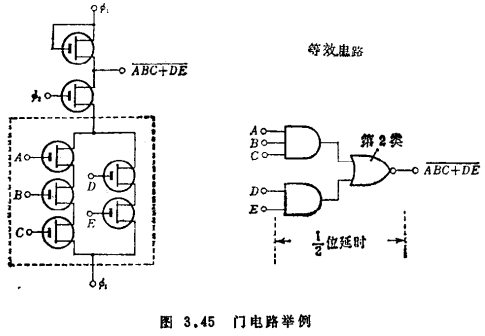

如图3.45所示,将第二类的用虚线框起来的部分,改为晶体管的串并联接法,则为A、B、C三输入端的“与门”电路和D、E两输入端的“与门”电路,也就是![]() 的逻辑输出信号取样保持在输出端上。

的逻辑输出信号取样保持在输出端上。

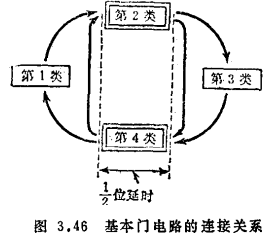

其它三种形式的基本电路,分别有将输出端预充电到L电平的时间t1或t3,对输入信号进行取样的时间t2或t4,所以可实现与第二类电路同样的动作,但各电路不可自由组合,四种基本电路之间有图3.46所示的连接关系。例如,第四类的门可用第一类或第四类的输出信号作为其输入信号,第二类的输出可驱动第三类和第四类的门。

多相时钟电路的特点是在全部时间内没有直流电流流过基本电路,亦即不产生直流通路。以第二类电路为例,无论在:Φ1的预充电的时间t1内,还是在Φ2的取样时间t2内,没有从电源到地的直流电流流过,而是通过负载电容C的预充电和放电进行逻辑运算。因此功耗极小。

如3.3.1节所述,两相电路的倒相器电路、门电路等电路的特性基本上由驱动晶体管和负载晶体管的gm决定;而在多相时钟电路中,所用的晶体管之间则毋需规定gm比。因此,往往称无比电路方式。另外对这种方式来说,可采用制造工艺能够容许的最小尺寸,用较小的布局面积即可实现复杂的门电路。

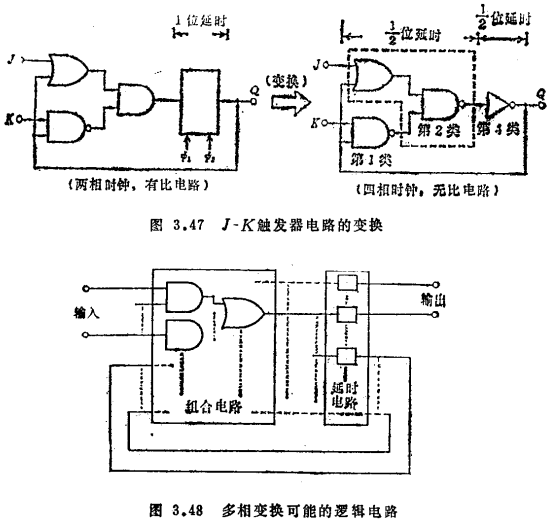

下面讲一讲由两相时钟电路向多相时钟电路的演变。门电路按图3.46连接时,在1个时钟周期内,信号可以通过的门电路的级数最大为4,最小为2。如将1个时钟周期看作是1位的时间,则第二类和第四类门电路有1/2位延时,第一类和第三类没有位延时,所以如就存储器功能而论,前者可以说是辅助性质的门。MOS集成多相时钟电路。譬如,两相时钟电路构成的J-K触发器电路可以变换成图3.47那样的电路。第二类门电路变换成较复杂的门之后,可以构成有多功能置位或复位条件的触发器电路。

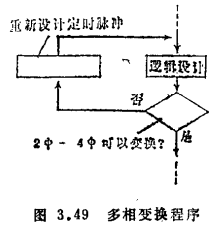

一般来说,图3.48所示的逻辑电路,亦即输入和输出间有1位以上延时的电路,理论上可以变换为多相时钟电路。但实际上,一个门的逻辑规模受最高工作频率的限制。在此限度内变换时,与两相时钟电路相比,所使用的门数目是相同的,但逻辑输出中往往有过剩的位延时。在这种场合,如图3.49所示,必须返回到逻辑设计阶段,进行适合于多相时钟电路的定时脉冲设计。这种再设计工作,一般要返回到系统设计的阶段。

所有逻辑电路可看作是由组合电路和存储电路组合成的。MOS集成多相时钟电路。组合电路本身并不能变换使门有位延时的多相时钟电路,接到组合电路输入端和输出端的是存储电路或输入输出装置,它们可以吸收或利用变换所产生的过剩位延时。当这么做有困难时也可以用加很长的位延时的方法将该电路变换成多相时钟电路。

上述的四相电路方式,需要令整个系统的结构都统一成该种电路,所以很少有中小规模集成电路的产品,大部分在大规模集成电路中采用。