电子技术论坛

信息来源: 时间:2021-4-25

MOS集成计数器电路图及工作原理详解分析

前节的二进制触发器电路,输入一组“0”“1”的脉冲,也就是输入一位输入脉冲之后,输出才翻转。因此,可以得到重复1/2输入周期的输出。MOS集成计数器电路图。从而当这些触发器电路级联时,可以构成二进制计数电路,该电路从初级起各级具有20、21,22、…2n的二进制编码权。设输入脉冲的频率为fi,级联的级数为n,则最末级输出脉冲的重复频率为

为了得到任意的n进制计数电路,可向前级加反馈。在连成n级的计数电路,从第n级向第i级加反馈时,该电路等效于2n~(2i-1)级的计数电路。

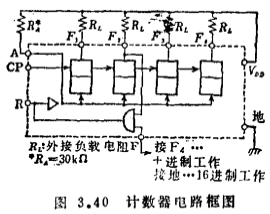

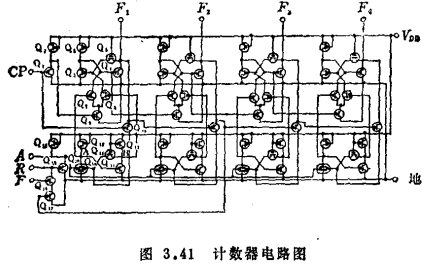

绘成图3.40的框图及图3.41的等效电路图的MOS集成电路,是十进制及16进制计数器。该电路由四级二进制触发器加控制门构成,如将反馈端(F)接地,即为16进的二进制计数器;如将反馈端(F)接输出端F4,则为十进制计数器。

首先用图3.41来说明第一级的二进制触发器电路的工作原理。为了便于叙述起见,将高电平视为“0”低电平视为“1”。MOS集成计数器电路图。Q3、Q4、Q5、Q6与其外接电阻R2以及Q10、Q11、Q12、Q13、Q14分别构成触发器电路(F/F)1和(F/F)2。Q1、Q2构成为输入信号提供反相信号的倒相器,Q16、Q17、Q18、Q19、Q20构成复位电路和十进制反馈电路。作为起始条件,今设(F/F)1、(F/F)2均保持在“0”状态。还假定复位端R开路,反馈端F接输出端F4。

在复位状态下,由于F1~F4的输出为“0”,Q16截止,Q19导通,Q20截止,所以不必考虑。

设(F/F)2的端点A和端点B分别处于“0”和“1”,(F/F1)通路上的Q7截止,Q8导通。为此,(F/F)1的Q3处于截止状态,Q4处于导通状态,输出端F1保持在“0”状态。

此处,如输入为“1”,则Q15导通,Q9截止,形成由(F/F)1向(F/F)2的反馈电路。结果,F1输出的“0”信号传输到Q10的栅,Q10由导通变为截止,端点A由“0”变到“1”,端点B由“1”变到“0”。再如输入为“0”,则Q9导通,Q15截止,构成由(F/F)2向(F/F)1的反馈电路。

因为端点A为“1”。所以Q7导通,Q4的栅通过Q7、Q9接地,(F/F)1翻转,F1的输出由“0”变为“1”。以后每当加输入脉冲时就重复相同的动作。MOS集成计数器电路图。第二级二进制触发器除了按第一级F1的输出信号及其翻转输出信号进行动作外,其它动作与前述完全相同。

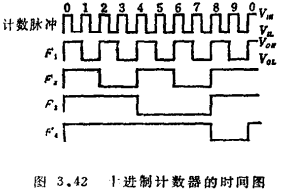

设输入脉冲为十个计数脉冲,因F2、F4同时为“1”状态,所以Q16、Q17导通,其结果Q19由导通变为截止,Q20及各级的复位晶体管导通,输出端F1~F4变为“0”状态而被复位。从而可得图3.42所示的十进制时间图。

和上述情形一样,如反馈端F接F1,就构成三进制计数器;反馈端接F3,则构成六进制计数器。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助